实验二集成逻辑门及其基本应用 2.2 利用门电路设计实现全加器功能

一、实验设计目标

(1)利用门电路设计实现全加器功能。

(2)通过此实验初步掌握连续赋值语句——assign语句的使用方法。

二、实验设计思路

在电路中,算术运算中的加减乘除运算,往往是分解转化为加法运算,因此,加法器是运算电路的核心。在做二进制的加法时,必须考虑低位向高位的进位。本实验设计实现一个全加器,输入信号包含两加数 、

、 ,以及进位输入

,以及进位输入 ,输出信号包含结果位

,输出信号包含结果位 以及进位输出

以及进位输出 。其中,进位输入

。其中,进位输入 为低一位加法运算产生的进位,进位输出

为低一位加法运算产生的进位,进位输出 将作为高一位加法运算的进位输入。表2.1给出了对应的真值表。从真值表可以写出

将作为高一位加法运算的进位输入。表2.1给出了对应的真值表。从真值表可以写出 与

与 的逻辑表达式:

的逻辑表达式:

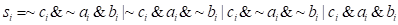

(2.1)

(2.1)

(2.2)

(2.2)

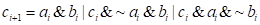

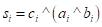

化简为:

(2.3)

(2.3)

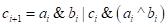

(2.4)

(2.4)

表2.1 全加器真值表

|

|

|

|

|

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

三、功能模块图与输入输出引脚说明

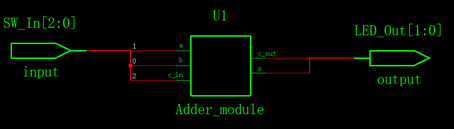

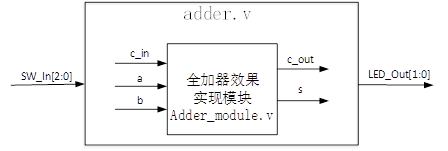

全加器工程包含顶层模块adder与底层模块Adder_module,图2.6是整个工程的模块功能图。下面介绍一下顶层模块各引脚的功能:

图2.6 全加器顶层原理图和模块功能图

(1)SW_In:拨动开关输入,共有三位。SW_In[2]、SW_In[1]和SW_In[0]分别连接“全加器”的输入信号c_in、a和b,用于模拟输入信号。

(2)LED_Out:输出到LED灯,共有两位。LED_Out[1]和LED_Out[0]分别连接“全加器”的输出信号c_out和s,通过LED灯的点亮或熄灭来表示全加器的运算结果。

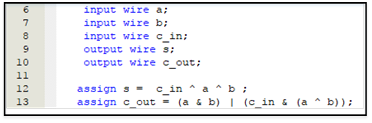

四、程序设计

图2.7是截取自底层模块Adder_module的部分代码:

6-10:信号输入输出端口及类型声明。

12-13:这是本次实验的重要程序,用于实现全加器功能,见公式(2.3)和公式(2.4)。

图2.7 全加器实验核心代码

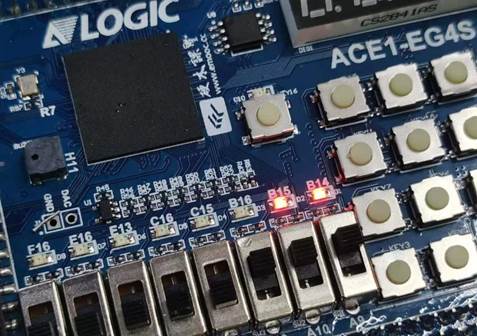

五、FPGA管脚配置

下面是Anlogic FPGA的IO Constraint,SW_In[2:0]输入信号分别与MINI_FPGA开发板上的SW2、SW1和SW0相连;LED_Out[1:0]输出信号分别与开发板上的LED1~LED0相连。

set_pin_assignment { LED_Out[0] } { LOCATION = B14; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[1] } { LOCATION = B15; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[2] } { LOCATION = B16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[3] } { LOCATION = C15; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[4] } { LOCATION = C16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[5] } { LOCATION = E13; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[6] } { LOCATION = E16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[7] } { LOCATION = F16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { SW_In[0] } { LOCATION = A9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { SW_In[1] } { LOCATION = A10; IOSTANDARD = LVCMOS33; }

set_pin_assignment { SW_In[2] } { LOCATION = B10; IOSTANDARD = LVCMOS33; }

六、实验结果

当SW2、SW1和SW0全部拨至“UP”位置时,此时 、

、 、

、 均为1,全加器运算结果为

均为1,全加器运算结果为 ,

, ,即LED1和LED0均点亮。其他情况请自行验证。

,即LED1和LED0均点亮。其他情况请自行验证。

七、思考与拓展

用四个全加器级联可以构成一个四位的加法器,只需将低位全加器的进位输出连接到高位全加器的进位输入即可,请编写程序在FPGA中实现四位加法器。