实验五 触发器 5.2 使用行为描述语句实现8D触发器

一、实验设计目标

(1)在FPGA中使用行为描述语句实现8D触发器功能。

(3)结合实验5.1与实验5.1,对比理解行为描述语句和结构描述语句的不同及各自的优点。

二、实验设计思路

输出在时钟信号某个特定时刻随输入改变的器件称为触发器。本实验设计实现一个带异步置位与清零端的正边沿触发的8D触发器,除包含8个数据输入端D7D0、和8个数据输出端Q7Q0外,其他功能均与实验5.1相同,此处就不再赘述。

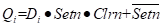

表5.1是第i组输入输出信号的真值表,从真值表可以写出 的逻辑表达式:

的逻辑表达式:

(5.1)

(5.1)

表5.1 8D触发器真值表

| 置位 | 清零 | 输入 | 输出 | |

|---|---|---|---|---|

|

|

|

|

|

| 0 | X | X | X | 1 |

| 1 | 0 | X | X | 0 |

| 1 | 1 |  |

0 | 0 |

| 1 | 1 |  |

1 | 1 |

三、功能模块图与输入输出引脚说明

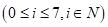

该工程包含顶层模块triggerD2与底层模块trigger_module,图5.5是整个工程的模块功能图。

图5.5 8D触发器模块功能图

下面介绍一下顶层模块各引脚的功能:

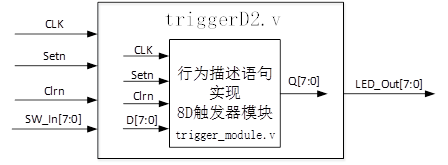

(1)CLK信号、Setn信号和Clrn信号的功能均与实验5.1中D触发器相同,但在本例中,如下图,Setn信号连接到Key_Col[0],Clrn信号连接到Key_Col[1]。这里我们将矩阵键盘的行信号(Key_Row[3:0])输出恒定的4’b0111,即Key_Row[3]始终为低,这样Key0按下时,Key_Col[0](FPGA的E11脚)由高变低,Key1按下时,Key_Col[1](FPGA的D11脚)由高变低。

(2)SW_In:拨动开关输入,共有八位。SW_In[7:0]分别连接“8D触发器”的数据输入“D7~D0”,用于模拟输入信号。

(5)LED_Out:输出到LED灯,共有八位。LED_Out[7:0]分别连接“8D触发器”的输出“Q7~Q0”,通过8个LED灯的亮灭情况来显示触发器的输出结果。

四、程序设计

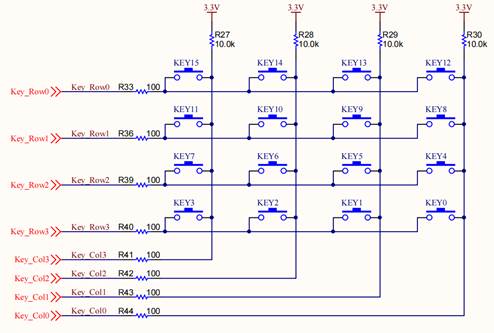

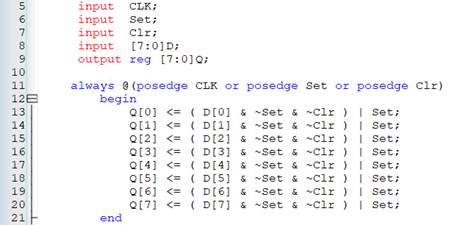

图5.6是截取自底层模块trigger_module的部分代码:

图5.6 8D触发器实验核心代码

5-9:输入输出信号声明。

11-21:使用行为描述语句实现带异步置位和清零端的8D触发器的逻辑表达式,见公式(5.1)。Setn信号的优先级高于Clrn信号。

五、FPGA管脚配置

以下 是Anlogic FPGA的IO Constraint,CLK信号、Setn信号和Clrn信号的配置方式均与实验5.1中相应信号的配置方式相同; LED_Out[7:0]输出信号分别与开发板上的LED7LED0相连;SW_In[7:0]输入信号分别与SW7SW0相连。

set_pin_assignment { CLK } { LOCATION = R7; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Clrn } { LOCATION = D11; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Key_Row[0] } { LOCATION = D9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Key_Row[1] } { LOCATION = F9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Key_Row[2] } { LOCATION = C10; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Key_Row[3] } { LOCATION = E10; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[0] } { LOCATION = B14; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[1] } { LOCATION = B15; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[2] } { LOCATION = B16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[3] } { LOCATION = C15; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[4] } { LOCATION = C16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[5] } { LOCATION = E13; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[6] } { LOCATION = E16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[7] } { LOCATION = F16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Setn } { LOCATION = E11; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Sw_In[0] } { LOCATION = A9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Sw_In[1] } { LOCATION = A10; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Sw_In[2] } { LOCATION = B10; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Sw_In[3] } { LOCATION = A11; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Sw_In[4] } { LOCATION = A12; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Sw_In[5] } { LOCATION = B12; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Sw_In[6] } { LOCATION = A13; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Sw_In[7] } { LOCATION = A14; IOSTANDARD = LVCMOS33; }

六、实验结果

当按键开关KEY0按下时,LED7~LED0均点亮;当按键开关KEY0不按下,KEY1

按下时,LED7LED0均熄灭;当按键开关KEY0,KEY1均不按下时,在每个时钟的上升沿,LED7LED0分别输出SW7~SW0的状态。因篇幅有限,置位与清零功能请自行验证。

七、思考与拓展

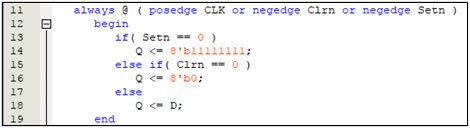

图5.8是使用if语句直接描述D触发器功能的实验代码,它不同于实验5.1

节从触发器的门级结构出发,也不同于实验5.3节从触发器的真值表出发,实际上在设计更为复杂的FPGA系统时,往往结合这几种方式,择优处理。请参考图5.8示代码自行建立工程实现8D触发器功能。

图5.8 if语句实现8D触发器参考代码

八、实验小结

(1)在本实验中,我们使用了非阻塞语句运算符“<=”代替阻塞语句运算符“=”。当使用阻塞运算符“=”时,赋值语句立即就把当前值赋给变量;但是,当使用非阻塞运算符“<=”时,赋值语句要等到always块结束时后,才完成对变量的赋值操作。

(2)行为描述语句可描述顺序执行或并行执行的程序结构,本节实验使用行为描述语言实现8D触发器功能,相较于实验5.1,程序更加直观、简洁,请结合实验5.1理解它们各自的特点和优势。