实验六 加法计数器

一、实验设计目标

(1)在FPGA中设计实现24进制加法计数器。

(3)通过此实验学习Anlogic_FPGA开发板上的数码管的使用方法。

二、实验设计思路

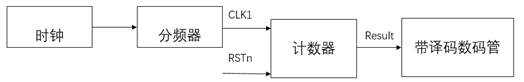

本实验设计实现一个24进制的加法计数器,它由晶体振荡器、分频器、计数器和数码管显示器组成,图6.1是该加法计数器的示意图。

图6.1 24进制加法计数器示意图

晶体振荡器产生稳定的50MHz的脉冲信号CLK,经过分频器后输出标准秒脉冲CLK1,作为计数器的计数时钟。计数器按照“00-01-02…22-23-00-01”的规律计数,每增加1秒,计数器加1,信号Result[7:4]代表计数器输出结果的十位,

Result[3:0]代表个位,RSTn为复位输入信号。将计数器的结果Result输出给数码管显示。

三、功能模块图与输入输出引脚说明

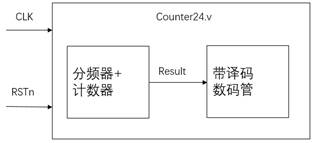

该工程包含顶层模块counter24与底层模块Accumulator_module、Digitron_NumDisplay_module。其中,Accumulator_module实现分频器和计数器的功能,Digitron_NumDisplay_module实现数码管显示器的功能。图6.2是整个工程的模块功能图。下面介绍一下顶层模块各引脚的功能:

图6.2 加法计数器模块功能图

(1)CLK:50MHz的时钟信号输入。将其分频后产生标准秒脉冲CLK1。

(2)RSTn:复位输入信号。低电平有效,复位后计数器输出Result变为00。

(3)DigitronCS_Out[3:0],Digitron_Out[7:0]:数码管的输出,共有四位片选和八位段选总线。

四、程序设计

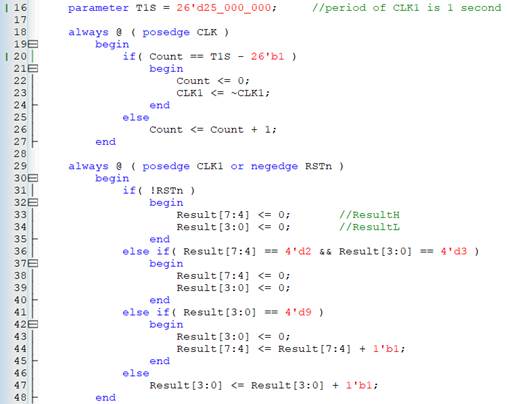

(1)图6.3是截取自底层模块Accumulator_module的部分代码:

16-24:CLK1是CLK通过分频代码产生的标准秒脉冲,周期为1s。

28-29:RSTn为0时,系统复位,计数器输出Result[7:0] 变为“00”。

31-42:这是一个24进制计数器,个位(Result[3:0])满10后向十位进位,

整体按照“23”翻“00”规律计数。

图6.3 Accumulator_module核心代码

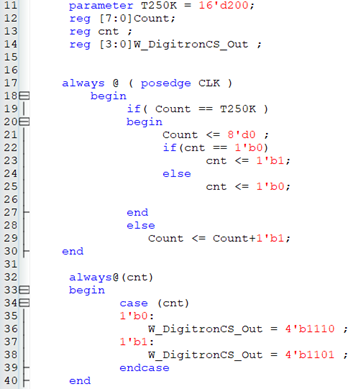

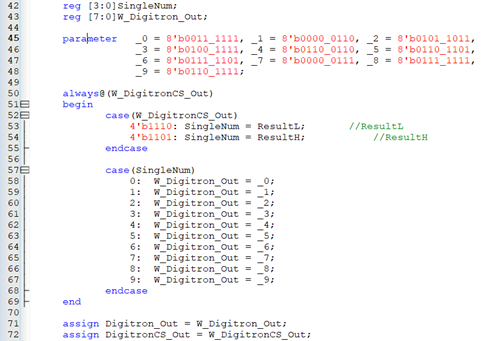

(2)图6.4是截取自底层模块Digitron_NumDisplay的部分代码:

11-40:分频和数码管位选程序,使用Count产生250KHz的扫描频率,每个扫描周期改变数码管位选W_DigitronCS_Out,这里数码管显示在低两位切换。

45-48:参数型常量定义。定义了“_0_1_2…_9”这九个输送到数码管的常量的值。

52-55:当数码管位选变化时,将该位上需要显示的值赋给SinleNum;

57-68:根据SingleNum的值,选择要显示的数字对应的LED段码赋给W_Digitron_Out;

五、FPGA管脚配置

下面是本例中Anlogic FPGA的引脚分配。

set_pin_assignment { CLK } { LOCATION = R7; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DigitronCS_Out[0] } { LOCATION = C9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DigitronCS_Out[1] } { LOCATION = B6; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DigitronCS_Out[2] } { LOCATION = A5; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DigitronCS_Out[3] } { LOCATION = A3; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[0] } { LOCATION = A4; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[1] } { LOCATION = A6; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[2] } { LOCATION = B8; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[3] } { LOCATION = E8; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[4] } { LOCATION = A7; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[5] } { LOCATION = B5; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[6] } { LOCATION = A8; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[7] } { LOCATION = C8; IOSTANDARD = LVCMOS33; }

set_pin_assignment { RSTn } { LOCATION = A9; IOSTANDARD = LVCMOS33; }

六、实验结果

当SW0拨至“UP”时的实验现象,数码管从00到23循环计数。当SW0拨至“DOWN”时,将显示“00”。

七、思考与拓展

(1)本实验初次使用数码管验证实验输出,认真阅读代码,理解数码管的驱动原理,这将在后面的实验中频繁出现。