实验八 功能数字钟

一、实验设计目标

在FPGA中设计实现一个多功能数字钟,具备以下功能:

(1)准确计时。能显示时、分、秒,小时的计时为24进制,分和秒的计时为60进制。

(2)校时功能。时、分可调。

(3)准点报时。当“时-分-秒”为“XX-59-50、XX-59-52、XX-59-54、XX-59-56、XX-59-58”时,蜂鸣器发“嘀”;当“时-分-秒”为“XX-00-00”时,扬声器发“嗒”。

二、实验设计思路

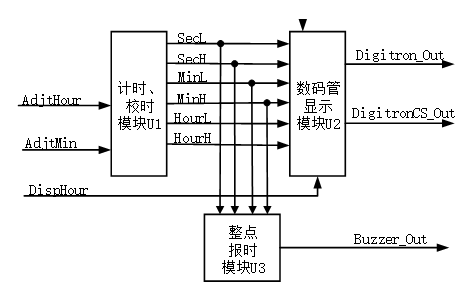

本节实验是在综合了前面几节实验知识点的基础上开展的,容易理解和掌握,该数字钟系统由计时、校时模块,数码管显示模块和整点报时模块组成,图8.1是该系统的示意图。

图8.1 数字钟系统示意图

计时、校时模块能工作于“计时”和“校时”两个状态。本模块内含一个分频电路用于产生标准秒脉冲。设置3个开关用于调整时间,包括小时调整开关AdjtHour和分钟调整开关AdjtMin,当其有效时,模块停止计时,工作于“校时”状态。输出信号包括秒个位SecL、秒十位SecH、分个位MinL、分十位MinH、时个位HourL、时十位HourH。

数码管显示模块用于显示“时、分、秒”。Anlogic_FPGA开发板上只有4个数码管,但要显示包括“时、分、秒”在内的6个时间信号,因此,我们增加一个“小时显示输入(DispHour)”信号,用于查看当前小时,高电平有效。当要调整小时,也需要使用数码管显示小时界面, AdjtHour信号便是用于告知这一点的。

整点报时模块的关键在于判断出当前时刻。使用if语句判断是否满足报时条件,通过改变输送到蜂鸣器上的导通信号的频率来改变蜂鸣器发声的频率,这在实验七中已经用到过,工作原理相同。

三、功能模块图与输入输出引脚说明

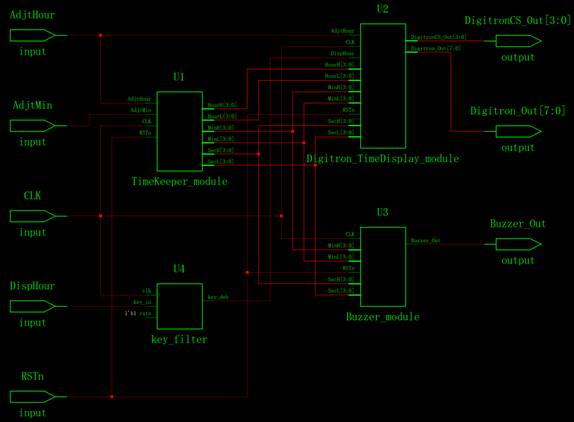

如上图,该工程包含顶层模块clock与底层模块TimeKeeper_module、Digitron_TimeDisplay_module和Buzzer_module。下面介绍一下顶层模块各主要引脚的功能:

(1)CLK:50MHz的基准时钟信号输入。将其50_000_000分频得到1HZ的数字钟工作频率CLK_1HZ。将其100_000分频得到500HZ的蜂鸣器报时频率“Di”,将其50_000分频得到1KHZ的蜂鸣器报时频率“Da”。将其200分频得到七段数码管的扫描频率。

(2)RSTn:系统复位输入信号,连接KEY0,低电平有效,我们将Key_Row置位4’b0111,当KEY0按下时,Key_Col[0]就输出低电平。复位后“小时-分钟-秒”置为“00-00-00”。

(3)DispHour:小时显示输入信号,低电平有效,我们将Key_Row置位4’b0111,当KEY1按下时,Key_Col[1]就输出低电平,经过按键消抖模块后,消抖模块的输出由低变高表示按键按下。当DispHour或AdjtHour信号有效时,数码管DIG3-DIG2显示当前小时,DIG1-DIG0显示当前分钟;当DispHour和AdjtHour信号均无效时,数码管DIG3-DIG0显示当前“分、秒”。

(4)AdjtHour 、AdjtMin:小时、分钟调节输入信号,高电平有效。当AdjtHour=1时,每来一个标准秒脉冲CLK_1HZ的上升沿,小时增加一。调整分钟开关相似。AdjtHour 、AdjtMin信号的优先级从左至右依次降低。

(5)Buzzer_Out:输出到蜂鸣器,通过改变输送到蜂鸣器的导通信号的频率,来改变蜂鸣器发声的频率,控制蜂鸣器产生“嘀、嗒”的报时声。

(6)Digitron_Out:七段数码管的段码显示输出,共有八位。

(7)DigitronCS_Out:数码管的片选信号,共有四位。扫描频率为250KHz。

四、程序设计

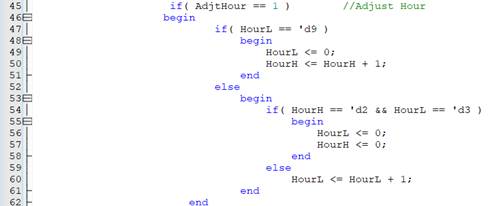

(1)图8.2是截取自底层模块TimeKeeper_module的部分代码,理解了此段程序则可以相应理解该模块的所有程序:

图8.2 TimeKeeper_module代码

45-62:当AdjtHour为1时,系统进入“校时”状态,开始调整“小时”。若时个位为9,则时个位清零并向时十位进位;若时十位、时个位为“23”,则时十位、时个位清零;若以上均不满足,则时个位加1,时十位不变。

五、FPGA管脚配置

以下是Anlogic FPGA的IO Constraint,CLK时钟输入信号、数码管片选信号DigitronCS_Out和数码管输出显示信号Digitron_Out的配置方式与实验六相同,DIG3DIG0依次显示“分、秒”,DispHour按下时DIG3DIG0依次显示“小时、分”;复位信号RSTn和小时显示信号DispHour分别与KEY0和KEY1相连;调整开关AdjtHour 、AdjtMin依次与SW0、SW1相连;Buzzer_Out信号输出到蜂鸣器引脚。

set_pin_assignment { AdjtHour } { LOCATION = A10; IOSTANDARD = LVCMOS33; }

set_pin_assignment { AdjtMin } { LOCATION = A9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Buzzer_Out } { LOCATION = H11; IOSTANDARD = LVCMOS33; }

set_pin_assignment { CLK } { LOCATION = R7; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DigitronCS_Out[0] } { LOCATION = C9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DigitronCS_Out[1] } { LOCATION = B6; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DigitronCS_Out[2] } { LOCATION = A5; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DigitronCS_Out[3] } { LOCATION = A3; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[0] } { LOCATION = A4; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[1] } { LOCATION = A6; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[2] } { LOCATION = B8; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[3] } { LOCATION = E8; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[4] } { LOCATION = A7; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[5] } { LOCATION = B5; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[6] } { LOCATION = A8; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Digitron_Out[7] } { LOCATION = C8; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DispHour } { LOCATION = D11; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Key_Row[0] } { LOCATION = D9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Key_Row[1] } { LOCATION = F9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Key_Row[2] } { LOCATION = C10; IOSTANDARD = LVCMOS33; }

set_pin_assignment { Key_Row[3] } { LOCATION = E10; IOSTANDARD = LVCMOS33; }

set_pin_assignment { RSTn } { LOCATION = E11; IOSTANDARD = LVCMOS33; }

六、实验结果

当SW1、SW0拨至“UP”时,分别调整“时、分”,且优先级从高到

低排列为SW0、SW1;KEY1按下时DIG3,DIG2显示“小时”,DIG1,DIG0显示分钟;KEY0按下时时钟复位,“时、分、秒”置为“00、00、00”;另有整点报时功能。

七、思考与拓展

(1)自行设计程序或查阅相关资料,实现以下功能:①显示“年-月”;②“定时闹钟”功能。