实验十五 高速ADC和DAC实验 15.1 高速ADC实验

一、实验设计目标

(1)编写程序,使用FPGA驱动ADDA开发板上的ADC工作。

二、实验设计思路

本实验设计使用FPGA驱动10位并行AD芯片工作,将正弦模拟信号转化为数字信号,并由FPGA内部逻辑分析仪观察得到的数字信号的波形。与实验二类似,AD实验的关键在于编写AD芯片的驱动程序和正确接收AD采集器输出的并行数字信号。

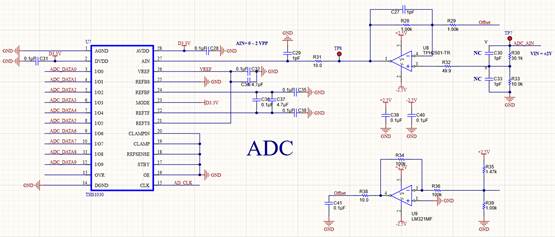

本次使用的是并行AD是TI的THS1030。THS1030是10位并行AD转换芯片,工作频率最高30MHz,拥有10个数据输出引脚(AD_DATA[9:0]),一个时钟输入引脚(AD_CLK),和模拟信号输入。(ADDA板也可以选择MS9280版本,和THS1030性能相同,管脚兼容)

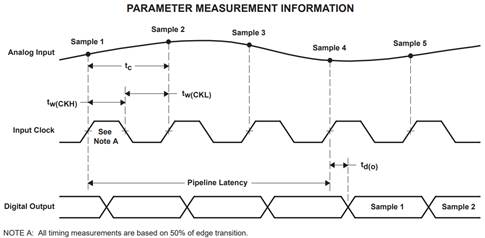

图3.1是该芯片的工作时序图。

图5.1 AD芯片工作时序图

可以看出,THS1030的工作比较简单,时钟输入后,数据经过流水线延时后即输出。我们只需要在驱动时钟的上升沿去读取ADC的输出数据就可以了。

对于所使用的ADDA开发板上的THS1030应用电路:

设定的输入范围为±2V,对应ADC的满量程输入为0-2V,因此输入电压Vin与输出码值Code之间的关系为:

Vin = 2 * Code * 2mV - 2V; 式(3.5)

三、功能模块图与输入输出引脚说明

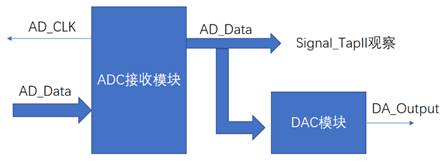

在理解了上述AD采集过程及转换规律后,设计AD采样系统如图5.3所示,AD接收模块用于驱动AD芯片完成上述采集过程。AD转换得到的数字信号送给Chip Watcher观察,验证电压公式,并送给R-2R DAC转换为模拟信号。R-2R DA电路参考电压与THS1030不同,所以产生的波形幅度会有所不同。

图5.3 HSAD采样系统示意图

(1)CLK:50MHz的基准时钟信号输入。

(2)RSTn:系统复位输入信号,低电平有效。

(3)AD_Data:AD数据输入信号。与AD芯片的DATA OUT引脚相连。

(4)AD_Clk:FPGA内部分频产生的时钟信号,输出给ADC的时钟输入引脚。

(5)DA_Data:DA的数字信号输入,因为DA只有8位,故取AD_Data的高8位送给DA_Data。

四、程序设计

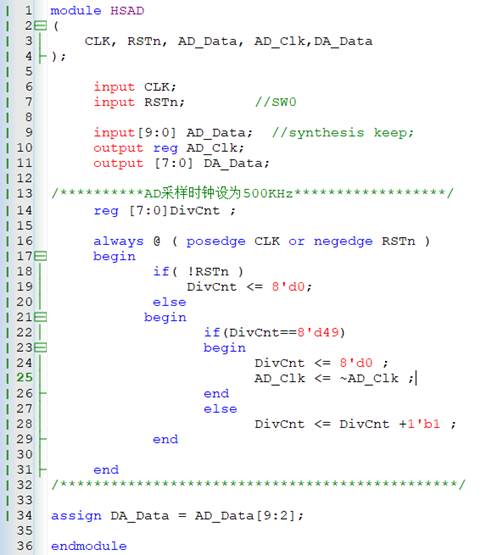

图5.5是截取自底层模块HSAD的部分代码:

图5.5 HSAD代码

16-33:将输入50MHz时钟分频到500KHz驱动ADC采样时钟

36:将ADC采集到的数值的高8位输出给板载R-2R DAC

五、FPGA管脚配置

以下是Anlogic FPGA的IO Constraint,CLK信号与开发板上的50MHz的晶振相连;RSTn信号接SW0;DA_A[7:0]分别送到R-2R电阻网络中。

set_pin_assignment { AD_Clk } { LOCATION = R5; IOSTANDARD = LVCMOS33; SLEWRATE = FAST; }

set_pin_assignment { AD_Data[0] } { LOCATION = N5; IOSTANDARD = LVCMOS33; }

set_pin_assignment { AD_Data[1] } { LOCATION = T12; IOSTANDARD = LVCMOS33; }

set_pin_assignment { AD_Data[2] } { LOCATION = R12; IOSTANDARD = LVCMOS33; }

set_pin_assignment { AD_Data[3] } { LOCATION = T9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { AD_Data[4] } { LOCATION = R9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { AD_Data[5] } { LOCATION = T7; IOSTANDARD = LVCMOS33; }

set_pin_assignment { AD_Data[6] } { LOCATION = T8; IOSTANDARD = LVCMOS33; }

set_pin_assignment { AD_Data[7] } { LOCATION = T5; IOSTANDARD = LVCMOS33; }

set_pin_assignment { AD_Data[8] } { LOCATION = T6; IOSTANDARD = LVCMOS33; }

set_pin_assignment { AD_Data[9] } { LOCATION = T4; IOSTANDARD = LVCMOS33; }

set_pin_assignment { CLK } { LOCATION = R7; IOSTANDARD = LVCMOS33; }

set_pin_assignment { RSTn } { LOCATION = A9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DA_Data[0] } { LOCATION = B14; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DA_Data[1] } { LOCATION = B15; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DA_Data[2] } { LOCATION = B16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DA_Data[3] } { LOCATION = C15; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DA_Data[4] } { LOCATION = C16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DA_Data[5] } { LOCATION = E13; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DA_Data[6] } { LOCATION = E16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DA_Data[7] } { LOCATION = F16; IOSTANDARD = LVCMOS33; }

六、实验结果

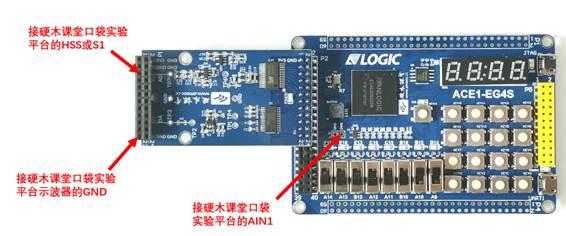

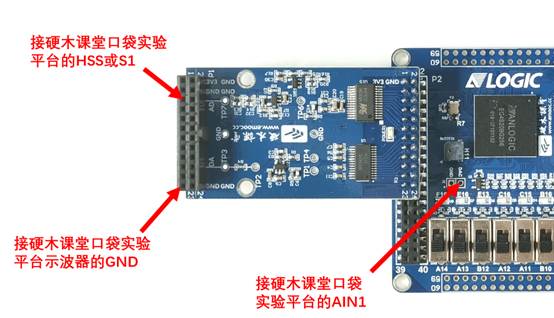

在验证实验时,ADDA开发板、EG4开发板和口袋仪器三者需要“共地”,使用口袋仪器的“信号源HSS或S1”向AD芯片送入正弦信号,板载R-2R DAC输出接口袋仪器的模拟输入端AIN1,口袋仪器的GND接ADDA开发板上的GND。

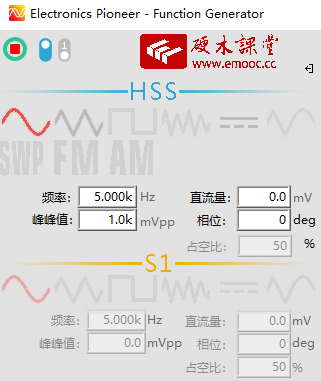

(1)图3.8是使用口袋仪器EPI-204系列产生的正弦信号的波形及参数说明。

图3.8 AD转换前的正弦信号

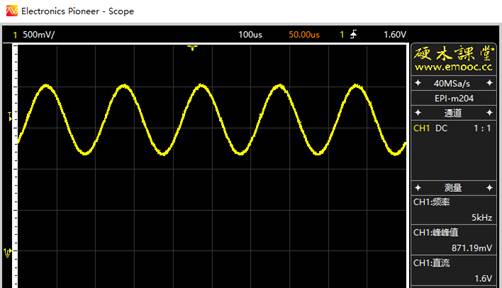

AD的数据传到R-2R DA模块上,给口袋仪器显示。。

图3.9 R-2R DAC输出的波形

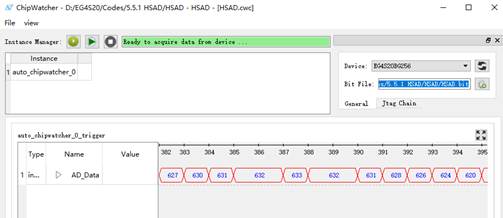

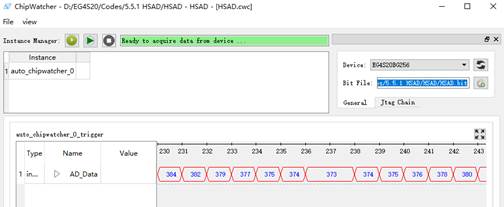

(2)图3.10是使用Chip Watcher观察到的经AD转换后的数据。通过式3.5换算,输入信号正好是±500mV的正弦波(可通过最大值633,最小值373换算)。

图**3.**10 Chip Watcher数据观察