组合逻辑电路

Welcome to 口袋实验!

数字电路之组合逻辑电路实验

实验目的

- 掌握组合逻辑电路的功能测试。

- 验证多数表决器的逻辑功能。

- 学会二进制数的运算规律。

More info: 组合逻辑

实验原理

- 功能描述:三人投票,两人或两人以上的相同投票结果为最终投票结果。

- 对应到逻辑描述:三人对应三个输入,0表示反对,1表示通过。输入为两个或两个以上0时,输出为0.输入为两个或两个以上1时,输出为1.

- 列出真值表

- 画出卡诺图

- 化简出逻辑表达式

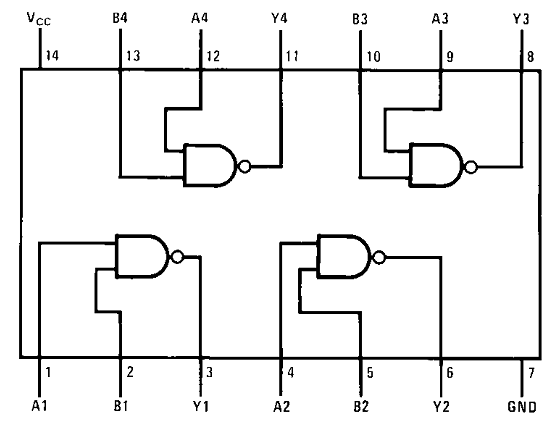

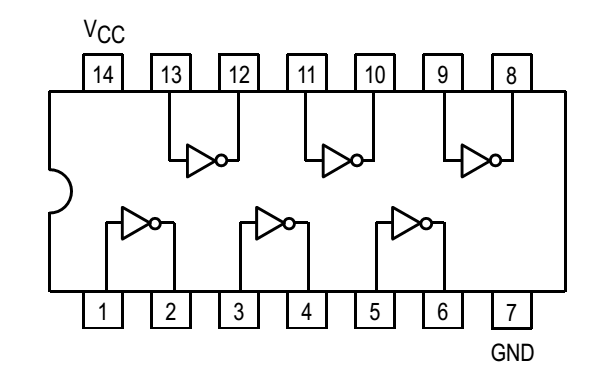

- 搭建逻辑门电路

- 测试

More info: 表决器

实验注意事项

- 确保连接导线是好的。可以用万用表测通断。或者实验箱上的蜂鸣器测通断

- 电路连接时先连接芯片的电压和地管脚,再连接其它管脚。

- 芯片的输入悬空为高时,不稳定,要接逻辑电平作为输入

- 芯片的输出不可以并联,不可以接地和电源

- 注意电源的正负

- 不要带电操作芯片的连接,断电后进行

More info: 安全操作

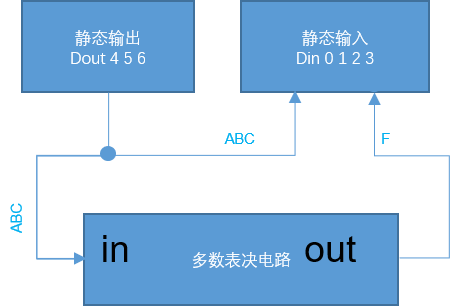

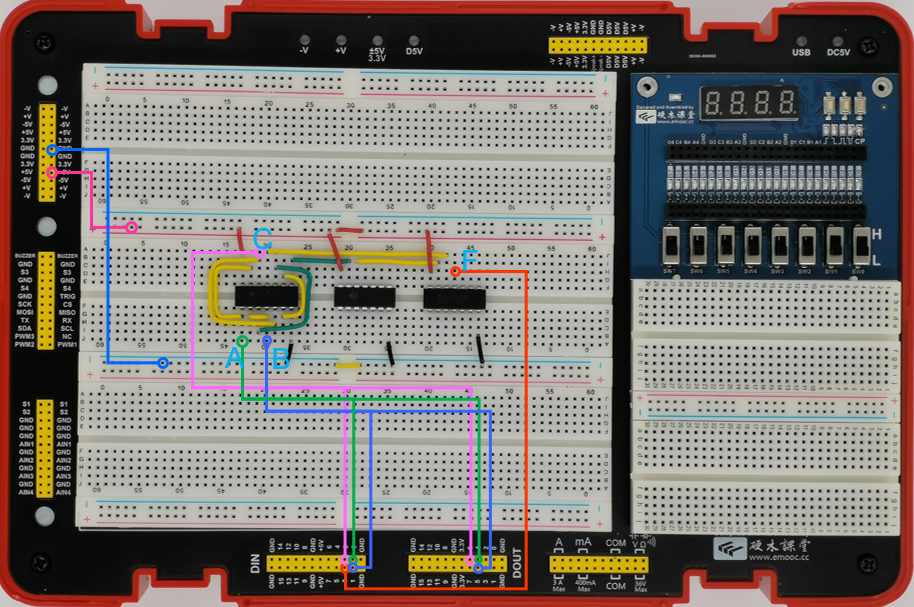

实验内容

- 用静态逻辑测试电路,将结果填写入真值表中,判断电路是否正确。

- 用脉冲信号产生和逻辑分析测试电路的时序图。根据波形填写真值表。并截图波形

More info: 真值表测试