D触发器及应用

Welcome to 口袋实验!

D触发器及应用

实验目的

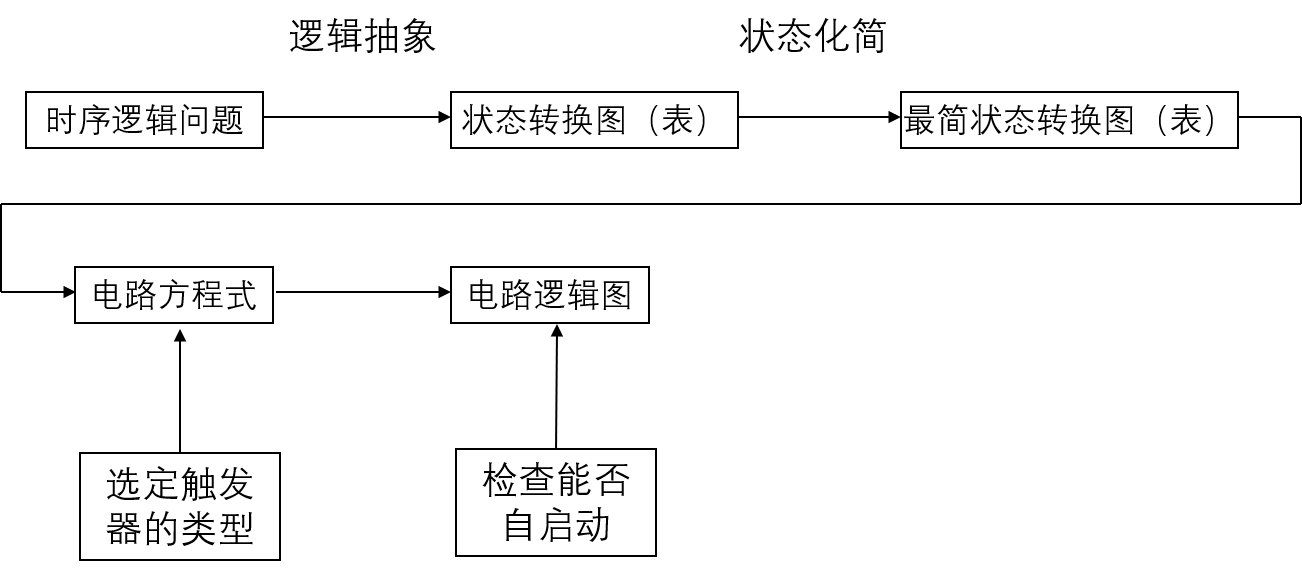

- 掌握同步时序逻辑电路的设计方法。

- 熟悉集成触发器的逻辑功能及使用。

More info: 同步时序

实验原理

实验注意事项

- 确保连接导线是好的。可以用万用表测通断。或者实验箱上的蜂鸣器测通断

- 电路连接时先连接芯片的电压和地管脚,再连接其它管脚。

- 芯片的输入悬空为高时,不稳定,要接逻辑电平作为输入

- 芯片的输出不可以并联,不可以接地和电源

- 注意电源的正负

- 不要带电操作芯片的连接,断电后进行

More info: 安全操作

实验内容

- 用D触发器设计一个异步计数器

- 同步十进制加法计数器设计举例(选做)

- 用D触发器设计一个同步四相时钟发生器(选做)

D触发器工程测试

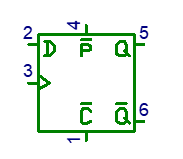

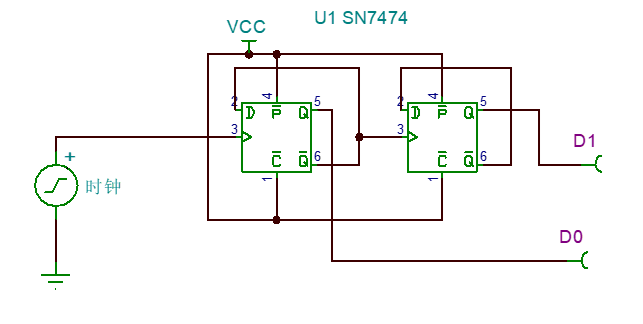

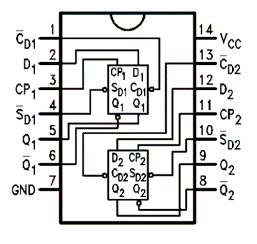

双D型触发器74LS74的逻辑符号如图所示。

- 图中 P 、C 端为异步置1端,置0端(或称异步置位,复位端)。3管脚为CP时钟脉冲端。

- 试按下面步骤做实验:

(1)分别在 P 、C 端加低电平,观察并记录Q、Q 端的状态。

(2)令P 、C 端为高电平,D端分别接高,低电平,用点动脉冲 作为CP,观察并记录当CP为0、↑、1、↓时Q端状态的变化。

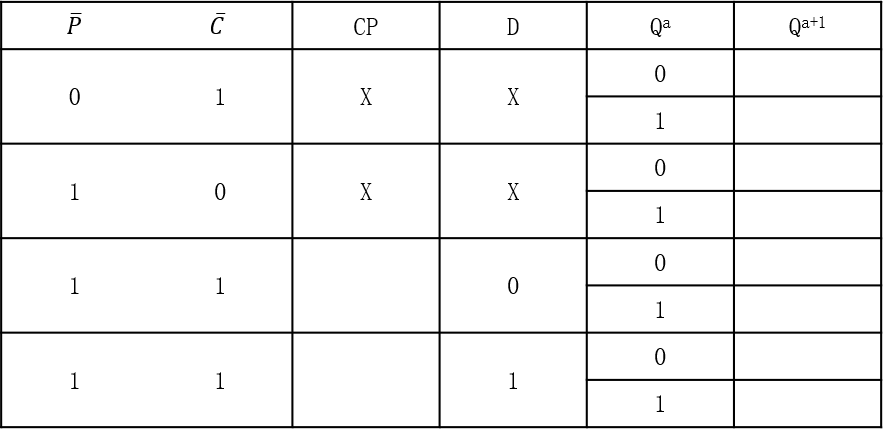

(3)当P = C = 1、CP=0(或CP=1),改变D端信号,观察Q端的状态是否变化? - 整理上述实验数据,将结果填入下表中。

(4)令P =C = 1,将D和Q 端相连,CP加连续脉冲,用双踪示波器观察并记录Q相对于CP的波形。

D触发器的逻辑功能测试表

D触发器异步计数器

- 时钟的产生方式

1.静态逻辑中边沿按钮产生Dout1

2.脉冲发生器,Dout0

3.数电板的边沿按钮

- 观察方式

1.静态逻辑中的数码管

2.逻辑分析仪

3.数电板的数码管

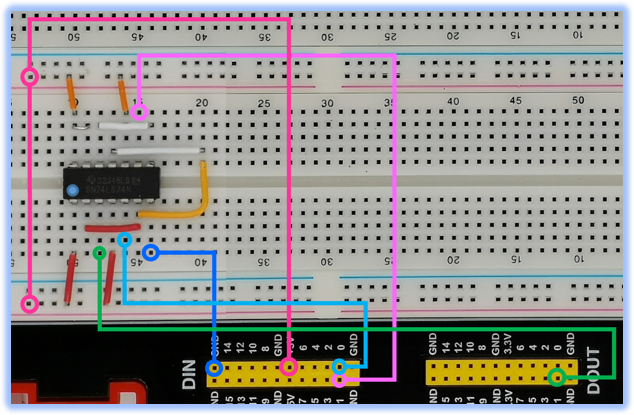

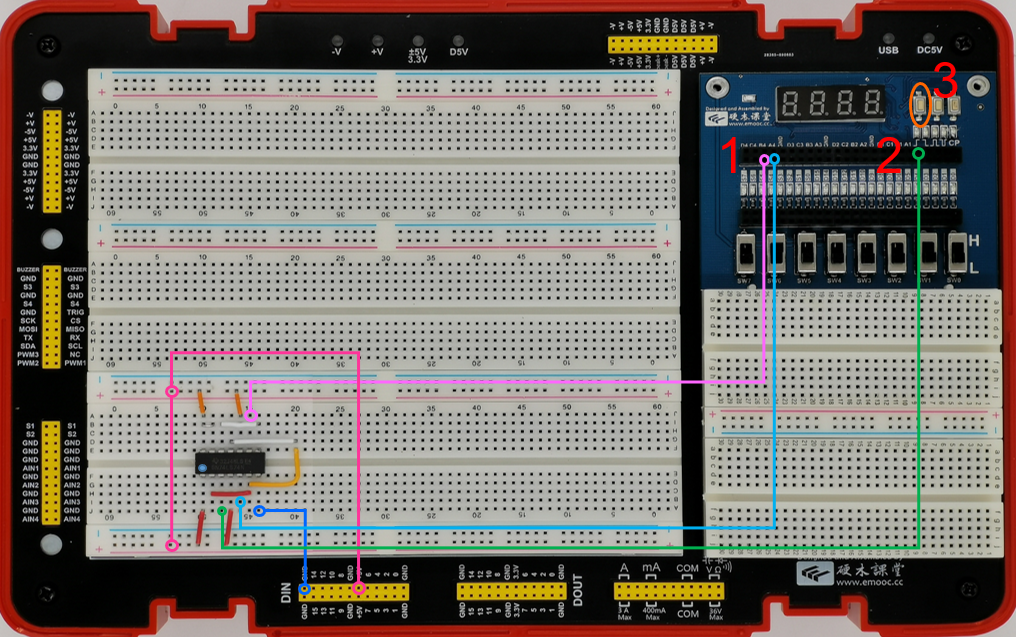

D触发器异步计数器电路搭建举例

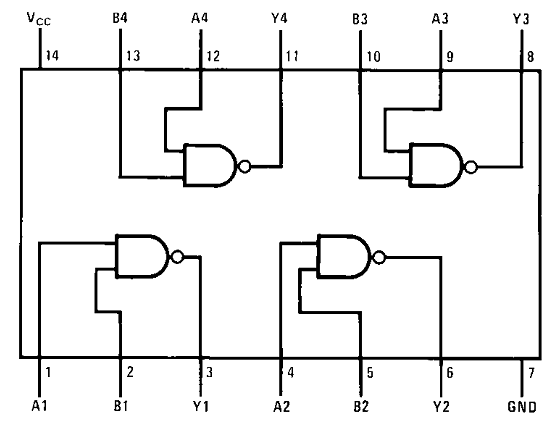

- Dout1接在74LS74芯片的时钟输入: 3管脚

- 74LS74的管脚5接Din0

- 74LS74的管脚9接DIn1

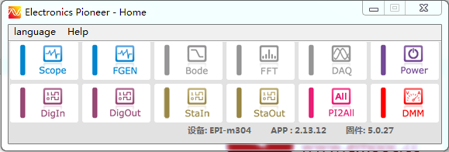

实验中仪器的使用

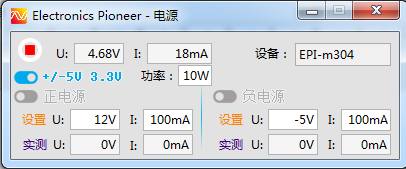

开启电源供电

1.打开电源

2.开启电源使能

2.打开正5V电源

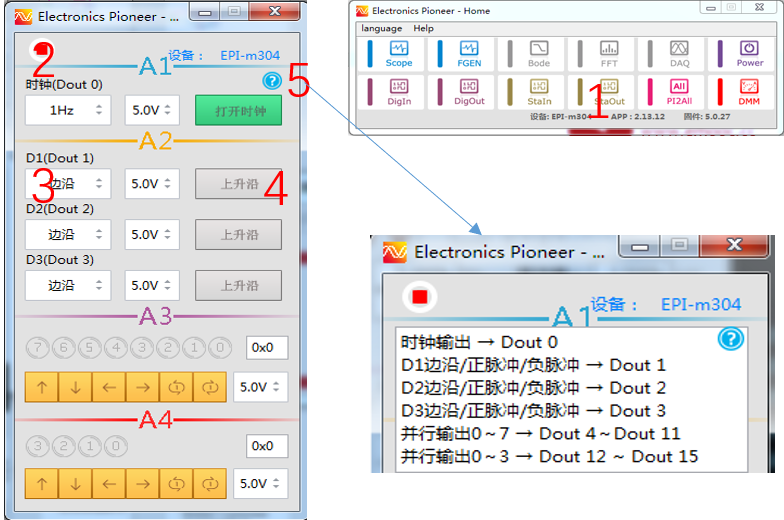

设置静态逻辑产生边沿

静态逻辑输出和输入,是用来模仿传统实验箱的按键和数码管,LED灯的。慢速时可以人眼观察。

打开静态输出

开启静态输出使能按钮

选择边沿

点击发出边沿。点击在上升沿和下降沿之间切换。

鼠标针放到

号上可以提示连接的对应关系。

号上可以提示连接的对应关系。

注意:

D1边沿对应Dout1 输出

Dout1接在74LS74芯片的3管脚时钟

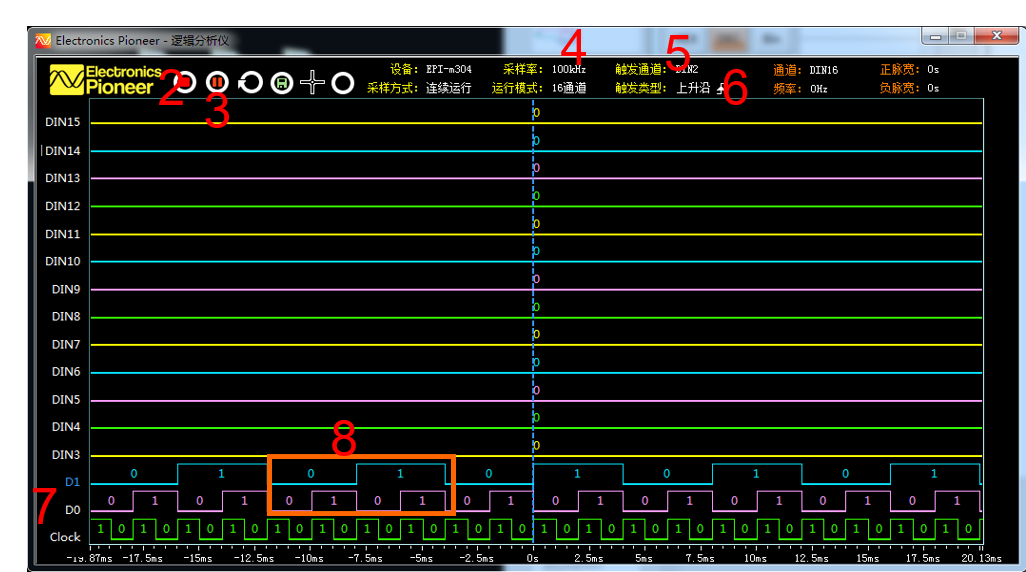

使用逻辑分析来观察

逻辑分析仪可以将输入和输出一起观察,看到电路整个时序图。

- 打开逻辑分析仪

- 点击使能按钮

- 点击开始运行

- 根据波形的疏密设置合适采样率。

- 选择DIN2作为触发通道

- 选择上升沿触发

- 双击,修改信号名称,给信号命名,便于使用。

- 其中的一个完整周期。0到3计数。

Dout0接Din0是作为clock

74LS74的管脚5接Din1

74LS74的管脚9接DIn2

使用数电板来做实验

- 开启电源+5V

- 将计数器输出接数电板的数码管

- 将时钟接数电板的边沿输出

- 按动边沿输出按钮

每按一次,可以看到计数值增1