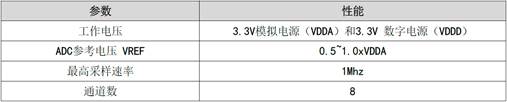

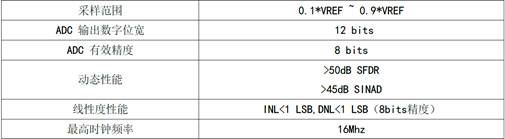

实验十五 高速ADC和DAC实验 15.2 THS5651A波形产生实验

一、实验设计目标

在完成了实验3.1的基础上,使用ADDA集成板上的THS5651A与THS1030联动,完成DAC波形发生和ADC采集实验。

二、实验设计思路

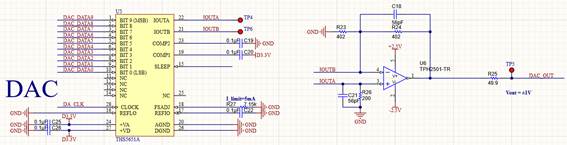

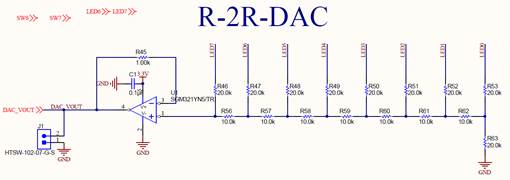

2.1 DAC电路计算

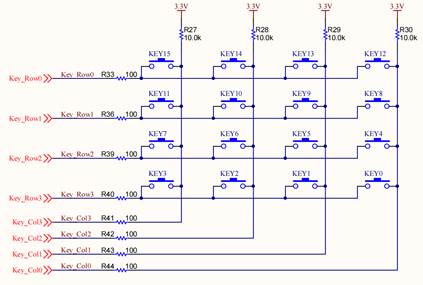

对于ADDA开发板上的THS5651A电路来说,通过R27和内部VREF设定的DAC输出差分电流是IOUTA = 0mA-5mA,IOUTB = 5mA-0mA(这里IOUTA和IOUTB是差分对),具体的输出电流值由输入DAC的码值DA_Data[9:0](也即是下文中的Code)确定。IOUTA和IOUTB通过外部运放电路转化为单端电压。计算过程如下:

VOUTA = IOUTA * RLOAD = Code/1024 * 5mA * 200Ω = 1V * Code/1024;

VOUTB = IOUTB * RLOAD = (1024-Code)/1024 * 5mA * 200Ω = 1V * (1-Code/1024);

DAC_OUT = VOUTA - VOUTB = (2*Code/1024 - 1) * 1V * 2 (运放提供两倍放大)

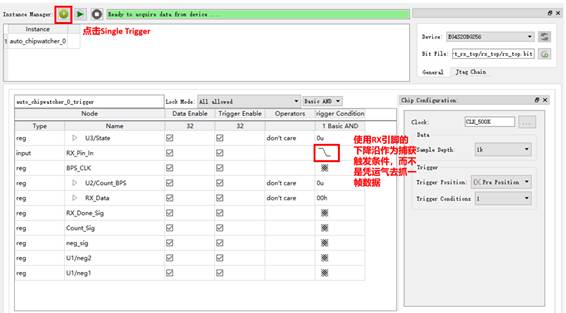

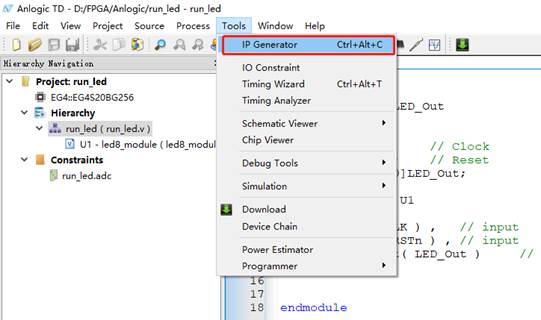

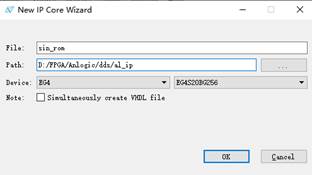

2.1 实验过程

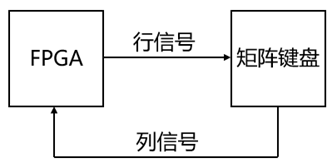

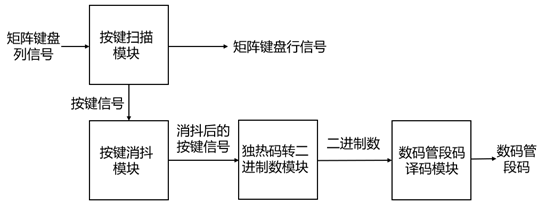

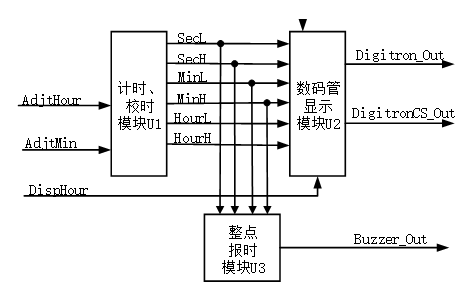

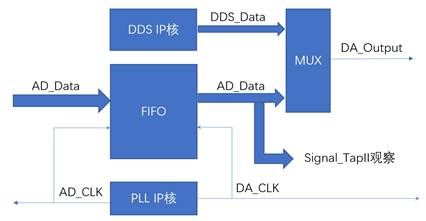

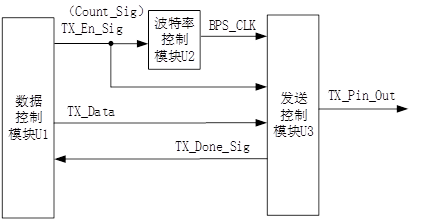

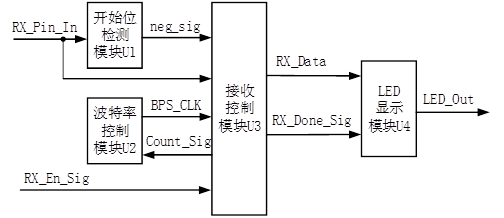

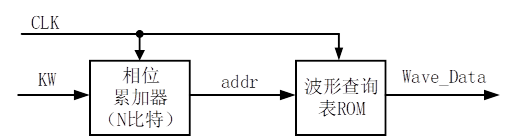

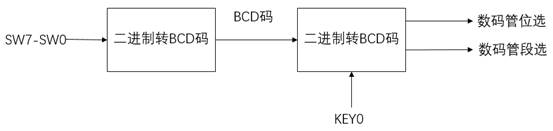

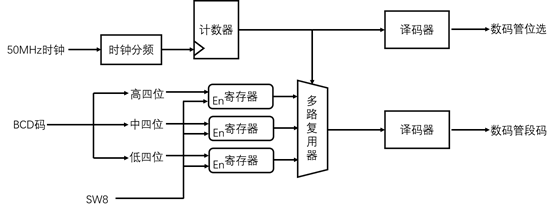

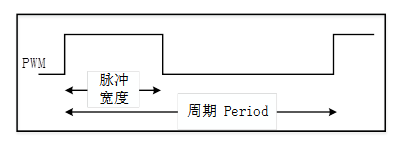

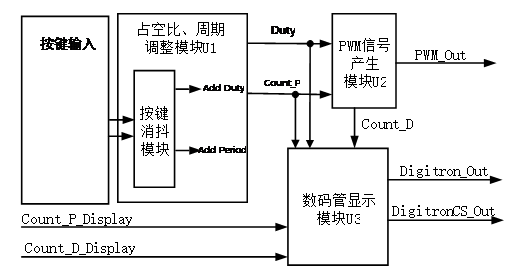

图3.2.1 实验整体框图

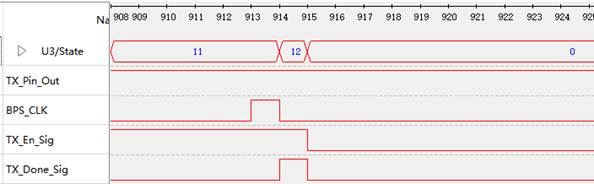

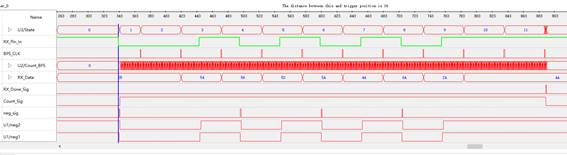

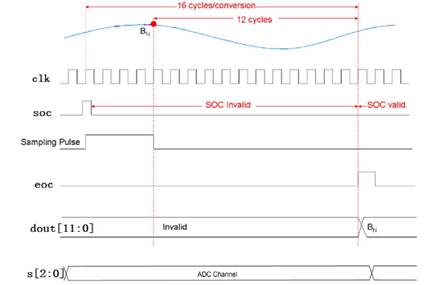

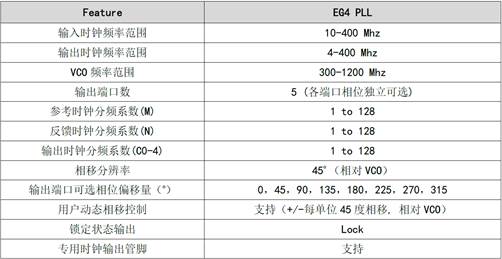

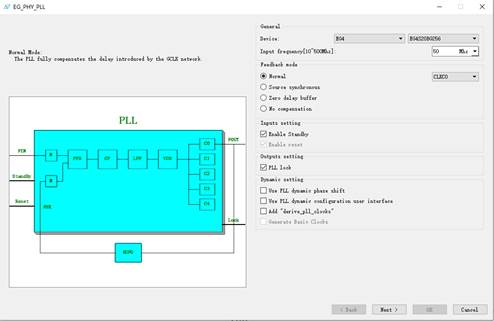

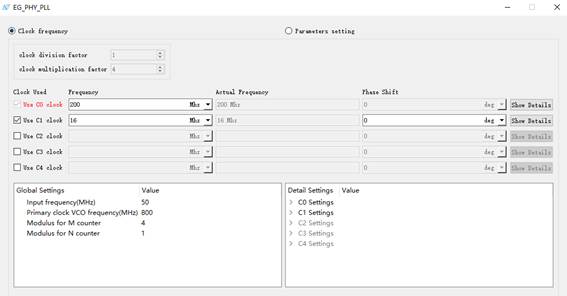

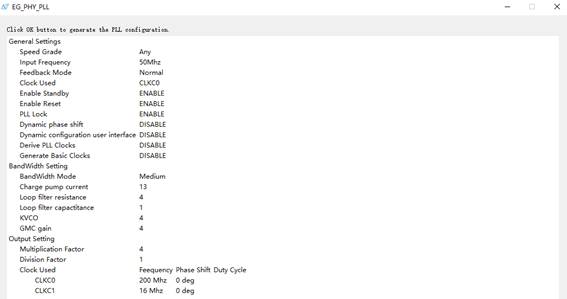

在此实验中,50MHz输入时钟通过PLL生成了ADC时钟和DAC时钟。ADC的采样时钟为40MHz(注意THS1030数据手册中额定的最高采样时钟为30MHz,如果波形出现毛刺,请降低采样频率试试),DAC的刷新时钟也为40MHz,在ADC和DAC的数据之间使用了一个FIFO来缓冲,避免跨时钟产生的数据毛刺。DAC的数据可以选择来自ADC采样的数值,也可以来自DDS IP核的输出。

三、功能模块图与输入输出引脚说明

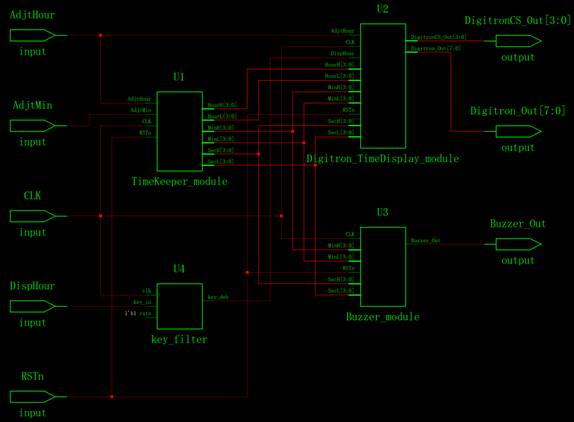

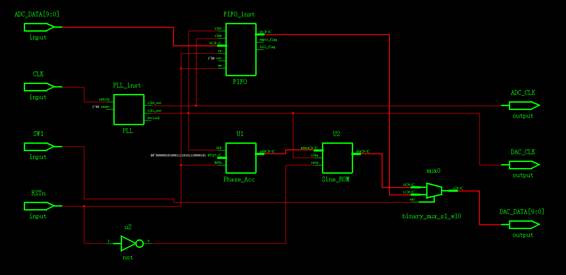

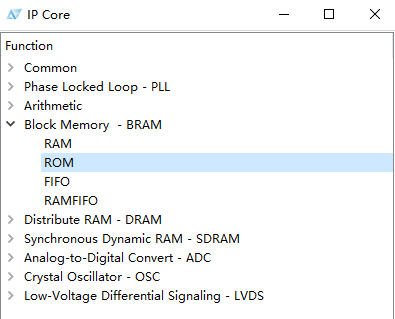

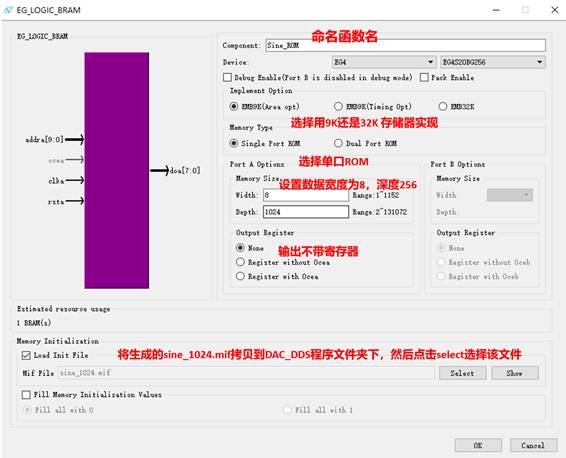

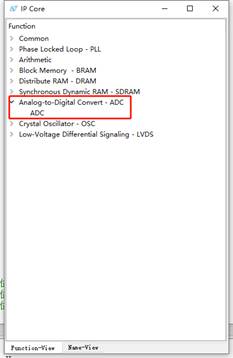

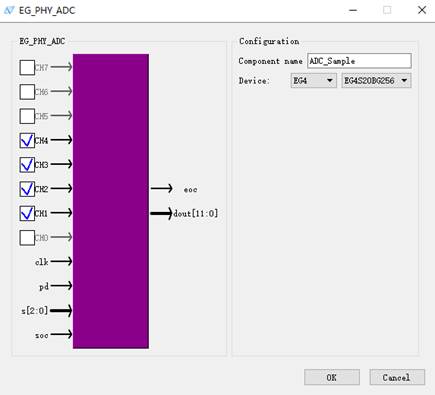

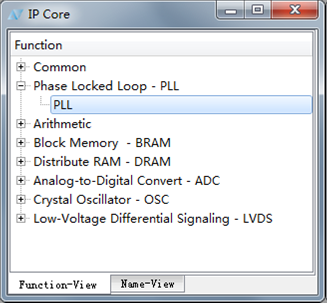

该工程包含顶层模块ADDA与相位累加器模块、IP核PLL,FIFO,ROM等。图3.2.2是顶层原理图,整个工程的模块功能图参考图3.2.1即可。下面介绍一下顶层模块各主要引脚的功能:

图3.2.2 ADDA顶层文件原理图

(1)CLK:50MHz的基准时钟信号输入。

(2)RSTn:系统复位输入信号,低电平有效,硬件。

(3)ADC_DATA[9:0]:ADC的输出数据

(4)DAC_DATA[9:0]:输出给DAC的数据

(5)ADC_CLK:CLK经过PLL模块后产生的ADC驱动时钟,40MHz;

(6)DAC_CLK:CLK经过PLL模块后产生的DAC驱动时钟,40MHz;

(7)SW1:选择DAC的数据源于ADC数据(SW1为高)或DDS模块(SW1为低);

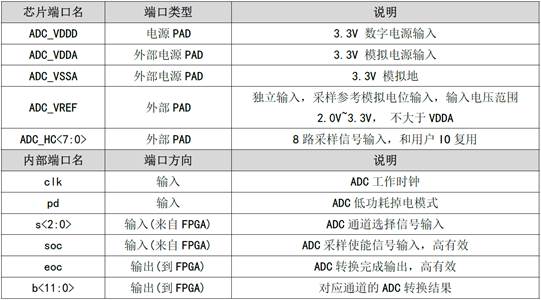

四、程序设计

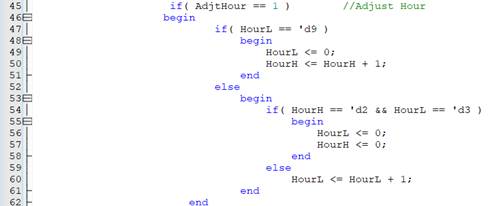

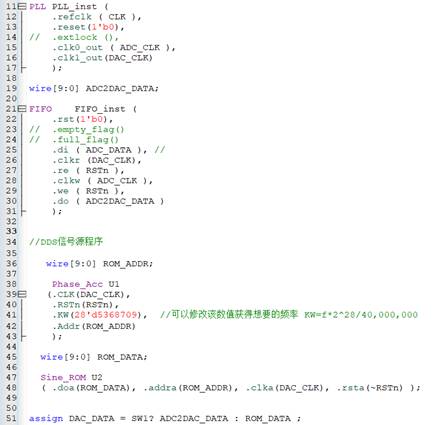

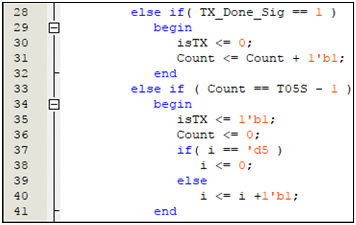

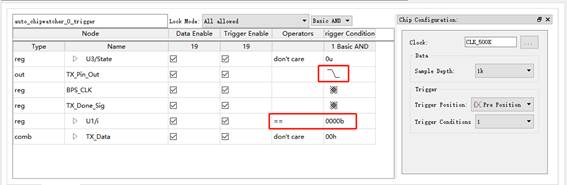

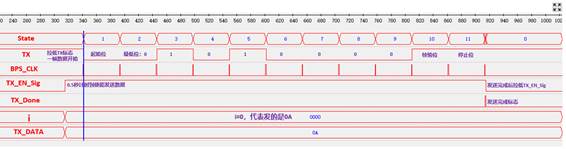

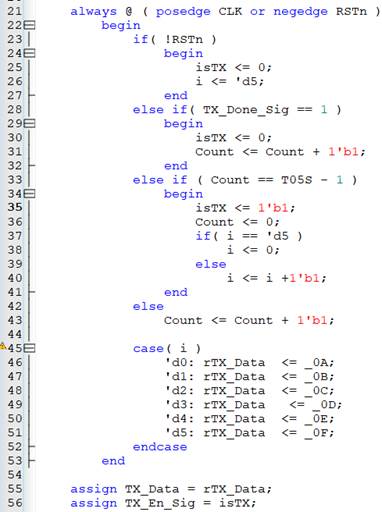

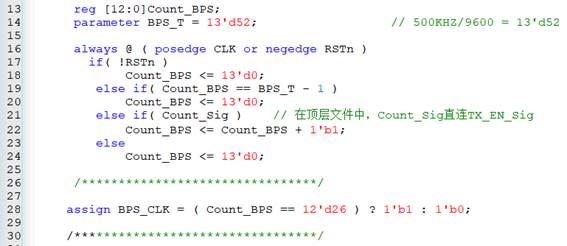

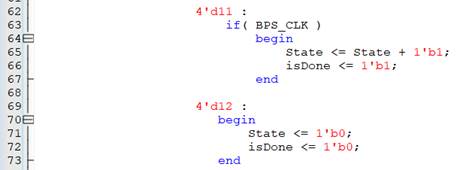

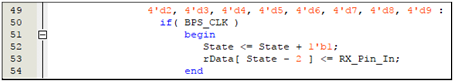

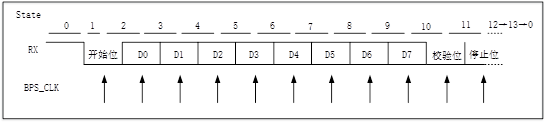

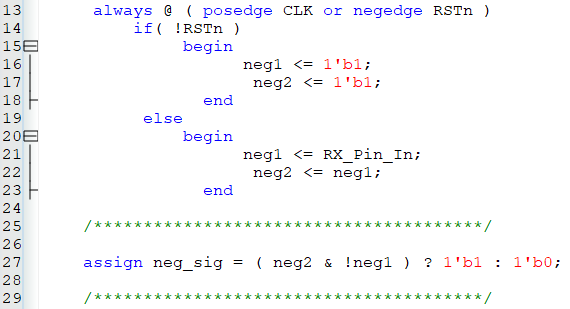

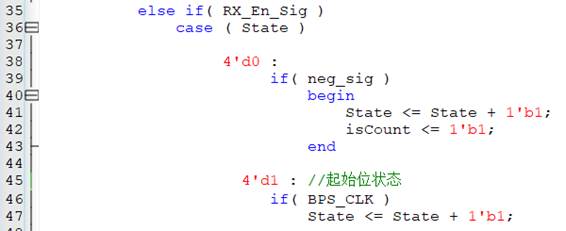

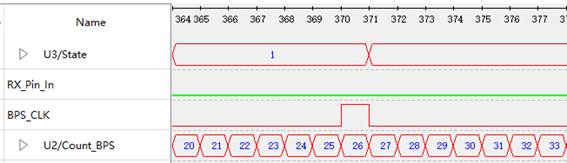

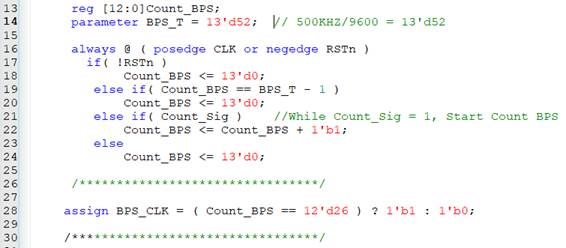

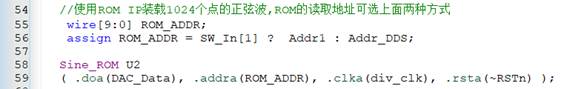

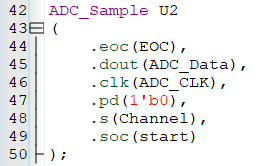

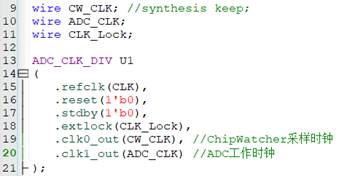

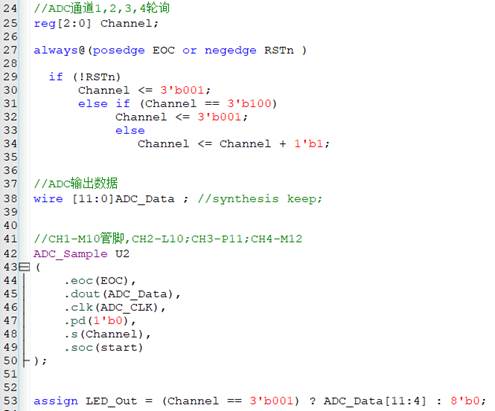

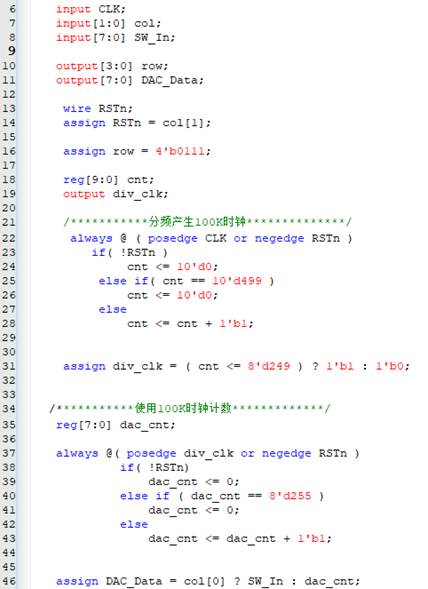

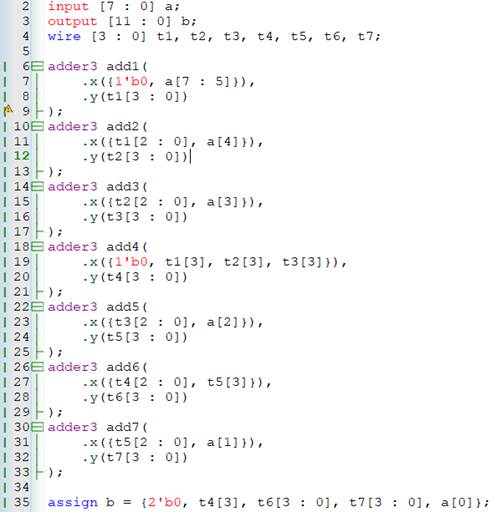

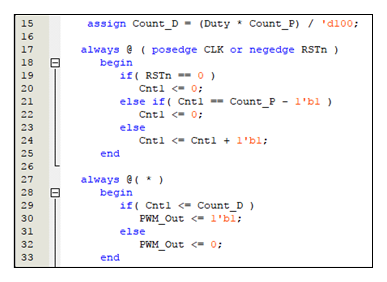

(1)图3.2.3是截取自顶层模块ADDA的代码,理解了此段程序则可以相应理解该模块的所有程序:

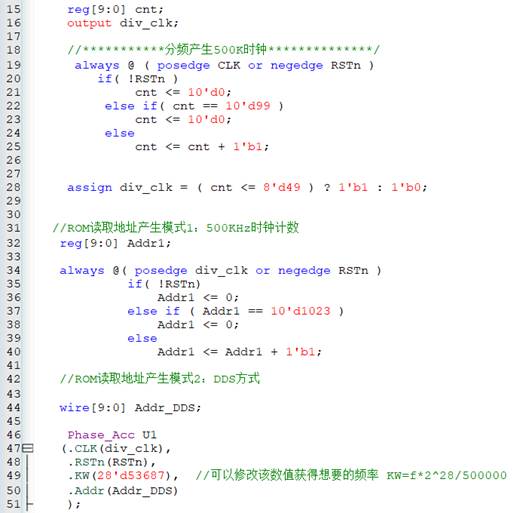

11 - 17:CLK经过PLL锁相环产生40MHz的ADC时钟和40MHz的DAC时钟;

21 - 31:数据缓冲FIFO,写时钟是ADC时钟,读时钟是DAC时钟,ADC的数据在ADC时钟的驱动下进入FIFO,ADC2DAC的数据在DAC时钟的驱动下输出FIFO;

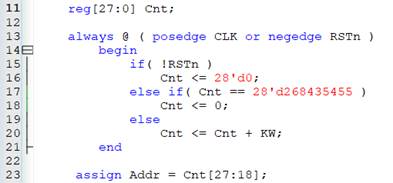

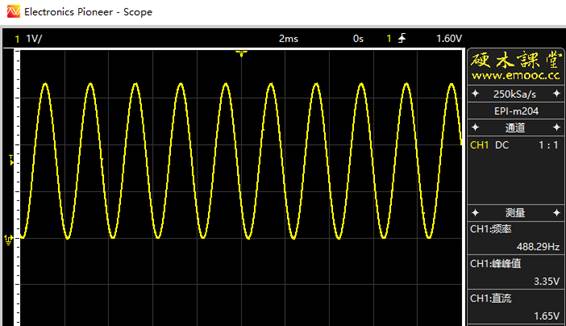

34 - 48:DDS核,用于产生一个数字正弦信号,输出频率由KW确定;计算公式为:fout = Fs * KW/2^28;这里Fs即PLL输出的DAC_CLK,40MHz;

51:通过SW1选择输出给DAC的数据来源;

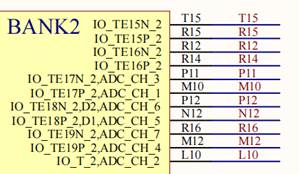

五、FPGA管脚配置

set_pin_assignment { ADC_CLK } { LOCATION = R5; IOSTANDARD = LVCMOS33; SLEWRATE = FAST; }

set_pin_assignment { ADC_DATA[0] } { LOCATION = N5; IOSTANDARD = LVCMOS33; }

set_pin_assignment { ADC_DATA[1] } { LOCATION = T12; IOSTANDARD = LVCMOS33; }

set_pin_assignment { ADC_DATA[2] } { LOCATION = R12; IOSTANDARD = LVCMOS33; }

set_pin_assignment { ADC_DATA[3] } { LOCATION = T9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { ADC_DATA[4] } { LOCATION = R9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { ADC_DATA[5] } { LOCATION = T7; IOSTANDARD = LVCMOS33; }

set_pin_assignment { ADC_DATA[6] } { LOCATION = T8; IOSTANDARD = LVCMOS33; }

set_pin_assignment { ADC_DATA[7] } { LOCATION = T5; IOSTANDARD = LVCMOS33; }

set_pin_assignment { ADC_DATA[8] } { LOCATION = T6; IOSTANDARD = LVCMOS33; }

set_pin_assignment { ADC_DATA[9] } { LOCATION = T4; IOSTANDARD = LVCMOS33; }

set_pin_assignment { CLK } { LOCATION = R7; IOSTANDARD = LVCMOS33; }

set_pin_assignment { DAC_CLK } { LOCATION = T15; IOSTANDARD = LVCMOS33; SLEWRATE = FAST; }

set_pin_assignment { DAC_DATA[0] } { LOCATION = T13; IOSTANDARD = LVCMOS33; SLEWRATE = FAST; }

set_pin_assignment { DAC_DATA[1] } { LOCATION = M6; IOSTANDARD = LVCMOS33; SLEWRATE = FAST; }

set_pin_assignment { DAC_DATA[2] } { LOCATION = P5; IOSTANDARD = LVCMOS33; SLEWRATE = FAST; }

set_pin_assignment { DAC_DATA[3] } { LOCATION = P6; IOSTANDARD = LVCMOS33; SLEWRATE = FAST; }

set_pin_assignment { DAC_DATA[4] } { LOCATION = N6; IOSTANDARD = LVCMOS33; SLEWRATE = FAST; }

set_pin_assignment { DAC_DATA[5] } { LOCATION = M7; IOSTANDARD = LVCMOS33; SLEWRATE = FAST; }

set_pin_assignment { DAC_DATA[6] } { LOCATION = L7; IOSTANDARD = LVCMOS33; SLEWRATE = FAST; }

set_pin_assignment { DAC_DATA[7] } { LOCATION = R14; IOSTANDARD = LVCMOS33; SLEWRATE = FAST; }

set_pin_assignment { DAC_DATA[8] } { LOCATION = T14; IOSTANDARD = LVCMOS33; SLEWRATE = FAST; }

set_pin_assignment { DAC_DATA[9] } { LOCATION = R15; IOSTANDARD = LVCMOS33; SLEWRATE = FAST; }

set_pin_assignment { RSTn } { LOCATION = A9; IOSTANDARD = LVCMOS33; }

set_pin_assignment { SW1 } { LOCATION = A10; IOSTANDARD = LVCMOS33; }

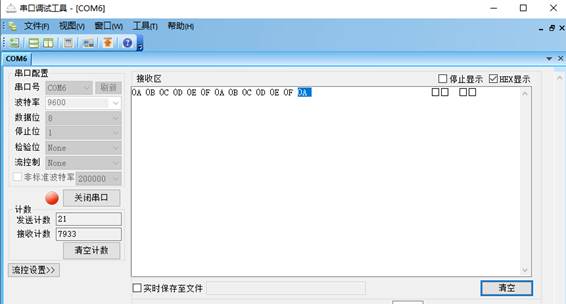

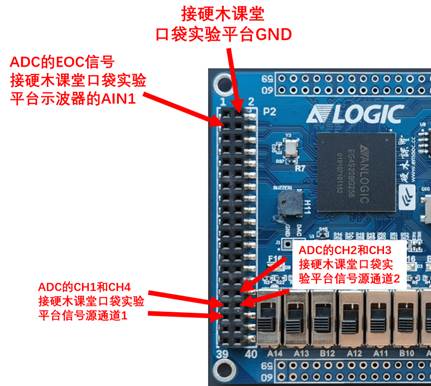

实验结果

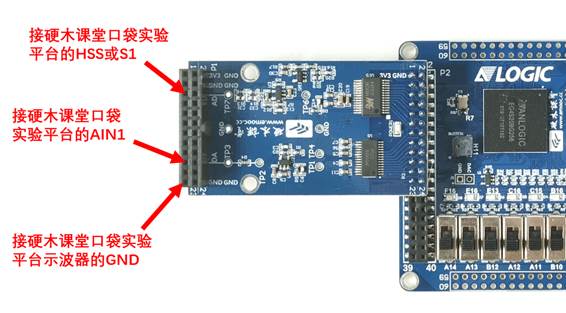

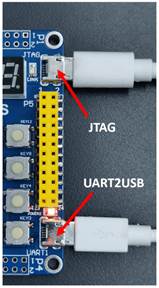

硬件连接图:

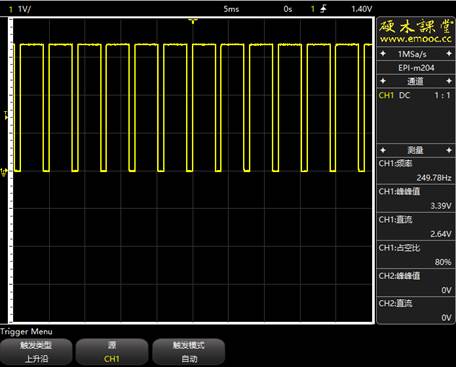

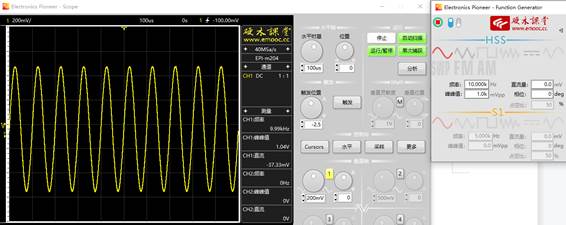

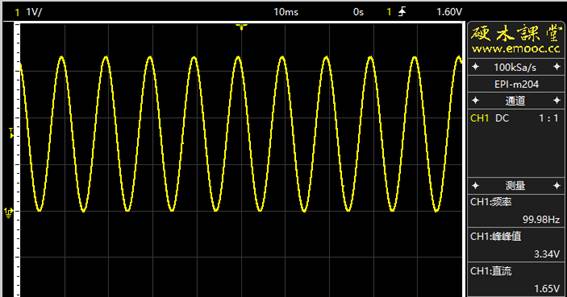

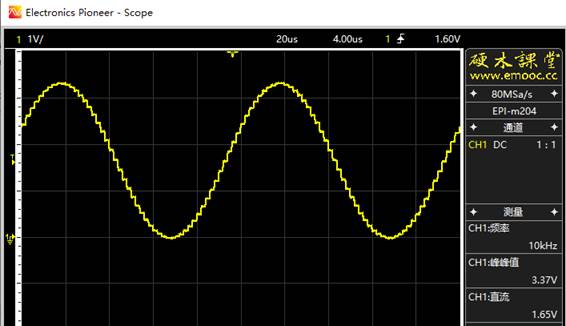

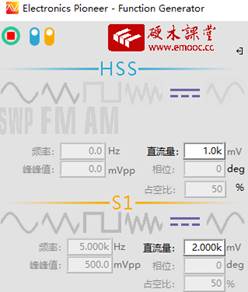

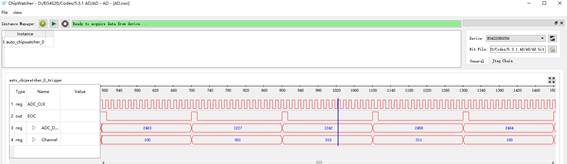

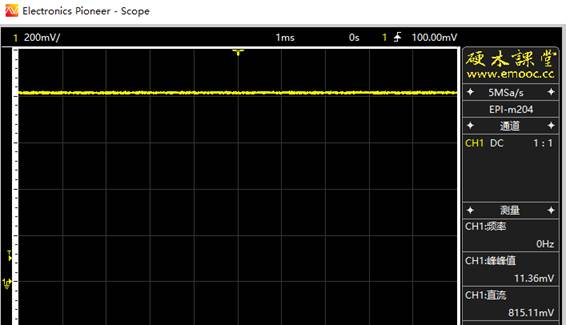

6.1 AD输入接口袋仪器的信号源输出,DA输出接口袋仪器的示波器输入,DA数据来源选择来自ADC的输出;可以看到输入10K,1Vpp,输出也是10K,1Vpp.

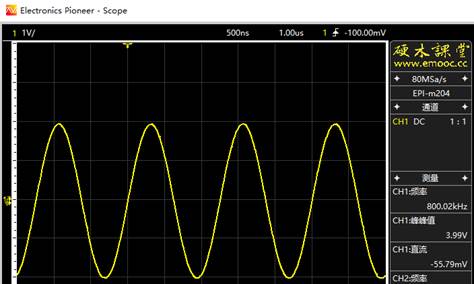

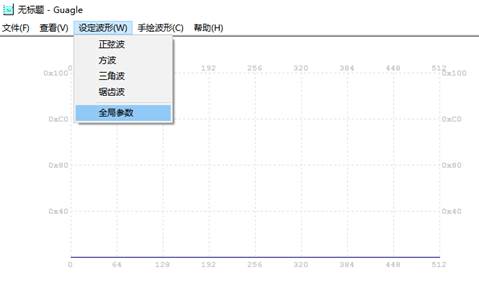

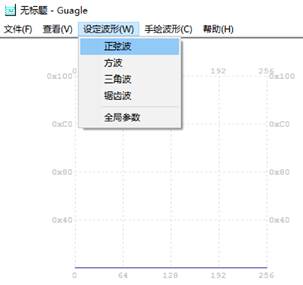

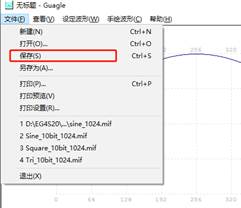

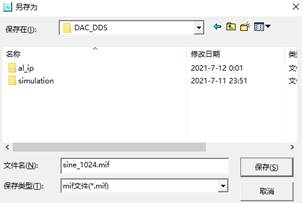

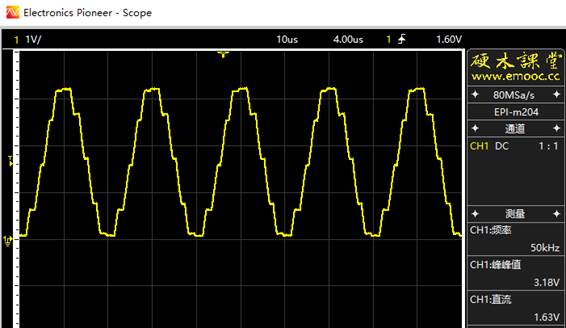

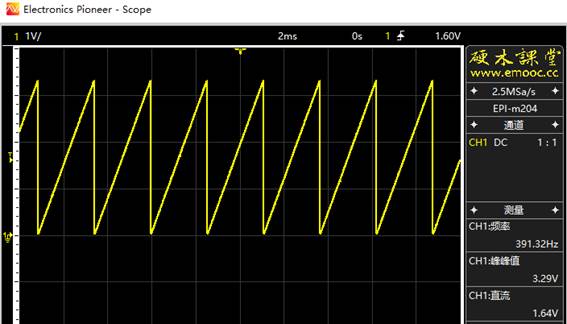

6.2 DA输出接AD输入同时送给口袋仪器的示波器观察,DA数据来源选择来自DDS;

七、思考

\1. 修改PLL模块,产生不同的ADC和DAC驱动时钟,观察在不同DAC时钟频率下DDS模块输出频率的改变;

\2. 修改KW值,产生不同频率的正弦信号。

(4.1)

(4.1)

(2.3)

(2.3)

(1.1)

(1.1)

(1.2)

(1.2)

)

)