大拇指安路FPGA开发板简介(Anlogic EG4S20BG256版本)

“大拇指”安路FPGA极简开发板是专门针对数字电路课程开发的,核心板不追求大而全,但已经覆盖数电课程的基础需求、简单易用并拥有较强的扩展性,结合学校一线教学经验和国产化趋势,我们将开发板的核心芯片型号选定为安路科技的EG4S20BG256,它资源丰富且管脚多;在外围功能模块的设计上,则以简洁直观、小巧易携带为目标,主要包括以下几类模块:板载USB-JTAG电路,实现一根线供电和调试;输出显示类,如LED灯、数码管;输入操作类的,如矩阵按键、拨动开关;发声及音频类的,如蜂鸣器;对外通信接口类的,如UART转USB接口;存储器类的,如FLASH存储器、SDRAM存储器;模数混合类的,如ADC和DAC。

基于FPGA的数字实验指导书

(Anlogic EG4S20BG256版本)

“大拇指”安路FPGA极简开发板是专门针对数字电路课程开发的,核心板不追求大而全,但已经覆盖数电课程的基础需求、简单易用并拥有较强的扩展性,结合学校一线教学经验和国产化趋势,我们将开发板的核心芯片型号选定为安路科技的EG4S20BG256,它资源丰富且管脚多;在外围功能模块的设计上,则以简洁直观、小巧易携带为目标,主要包括以下几类模块:板载USB-JTAG电路,实现一根线供电和调试;输出显示类,如LED灯、数码管;输入操作类的,如矩阵按键、拨动开关;发声及音频类的,如蜂鸣器;对外通信接口类的,如UART转USB接口;存储器类的,如FLASH存储器、SDRAM存储器;模数混合类的,如ADC和DAC。

1.1 大拇指安路FPGA开发板框架设计

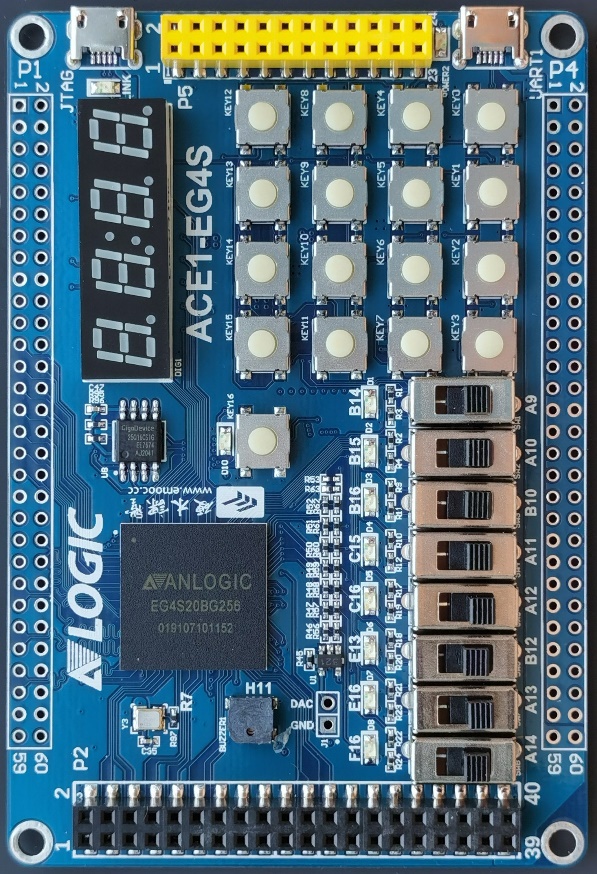

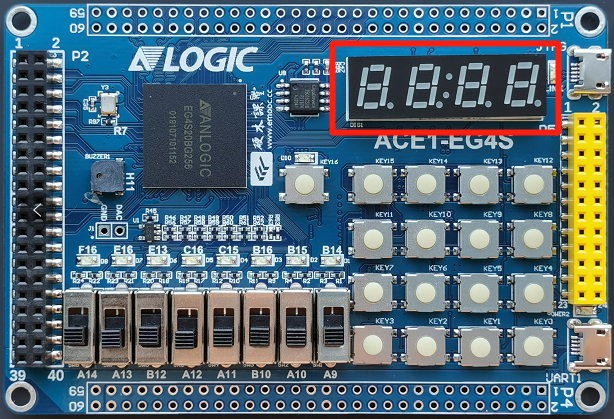

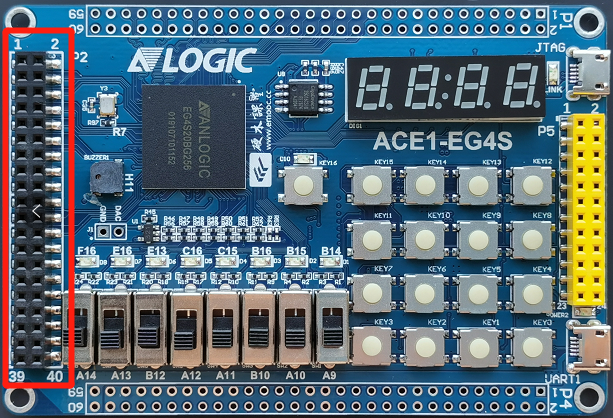

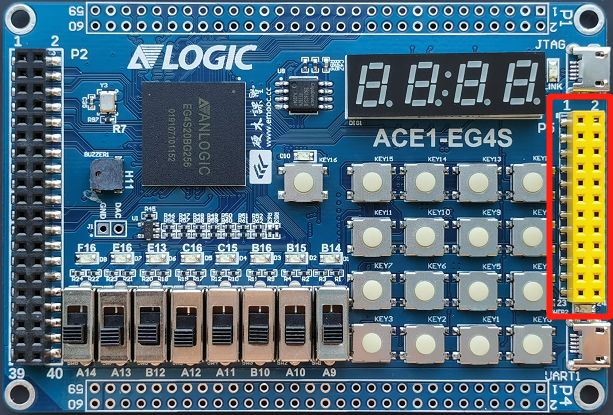

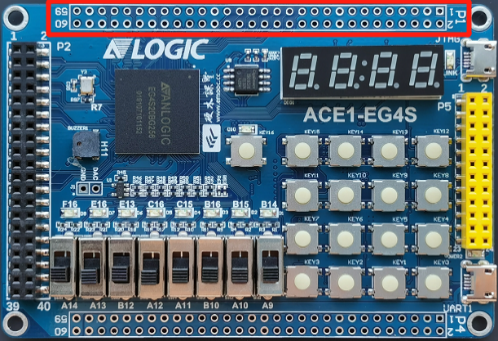

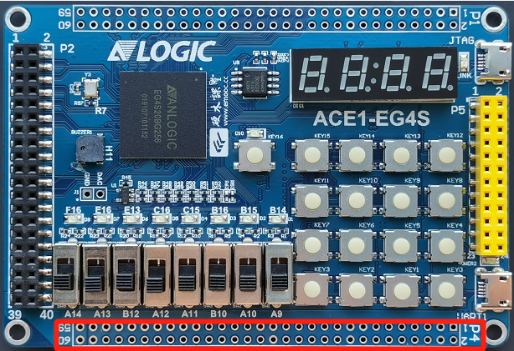

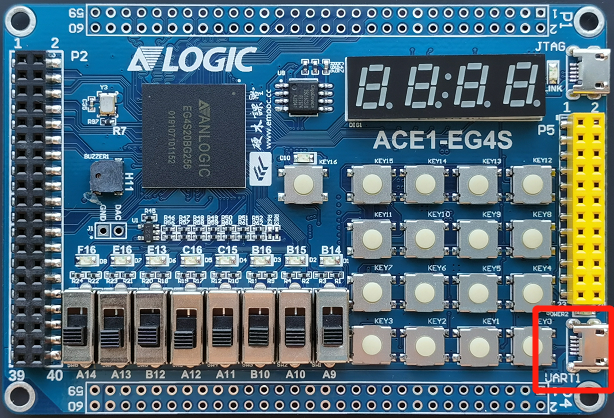

DMZ_Anlogic开发板如图1.1所示,主要包括三个部分:

(1)核心FPGA芯片:选用256个管脚的FPGA芯片EG4S20BG256。

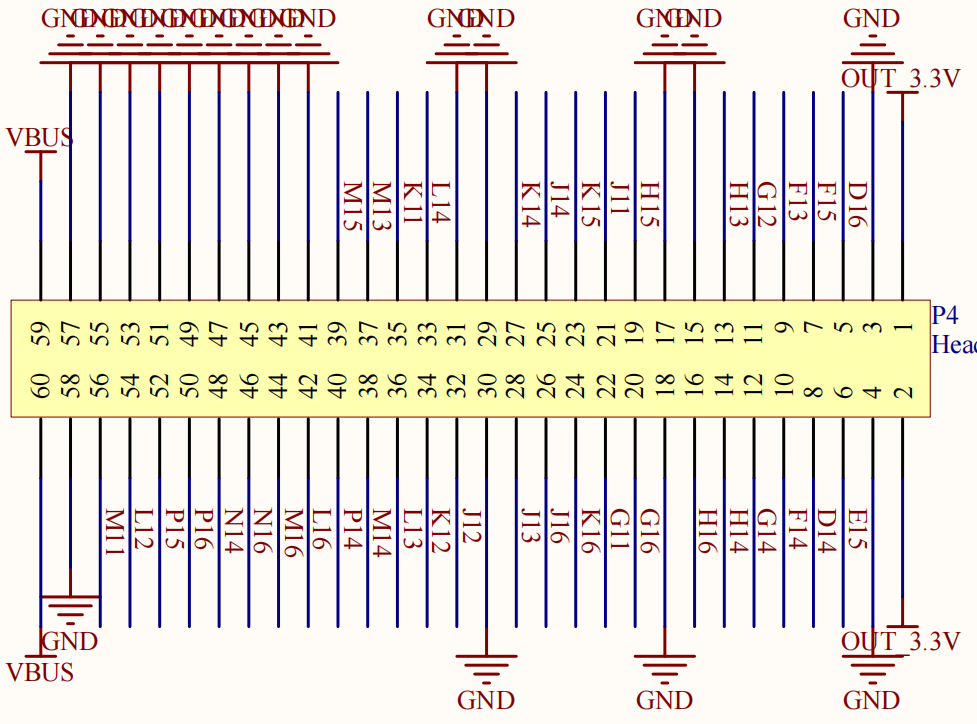

(2)外围设备。包含晶振、LED、数码管、蜂鸣器、按键开关、拨动开关、UART转USB接口,DAC电路等;开发板的上方(42个)、下方(37个)、左方(36个)、右方(22个)共有137个通用IO口,加上一定数量的GND或Power通道。

(3)USB转JTAG调试电路。实现一根USB线完成供电和调试。

图1.1是DMZ_Anlogic开发板的实物图。我们将在1.2节详细介绍FPGA芯片,在1.3节详细介绍各外围功能模块。

图1.1 DMZ_Anlogic开发板实物图正面

1.2 核心FPGA芯片简介

EG4是安路科技推出的“EAGLE

猎鹰”系列产品,具有低功耗、低成本、高性能等特点。丰富的LUT、DSP、BRAM、高速差分IO等资源,强大的引脚兼容替换性能。在工业控制、通信接入、显示驱动等领域可有效帮助用户提升性能、降低成本。EAGLE

系列 FPGA

定位低成本、低功耗可编程市场,面向大批量,成本敏感的应用,使系统设计师在降低成本的同时又能够满足不断增长的带宽要求。同时安路科技提供丰富的设计工具帮助用户有效地利用

EAGLE

平台实现复杂设计。业界领先的综合和布局布线工具,为用户设计高质量产品提供有力保障。

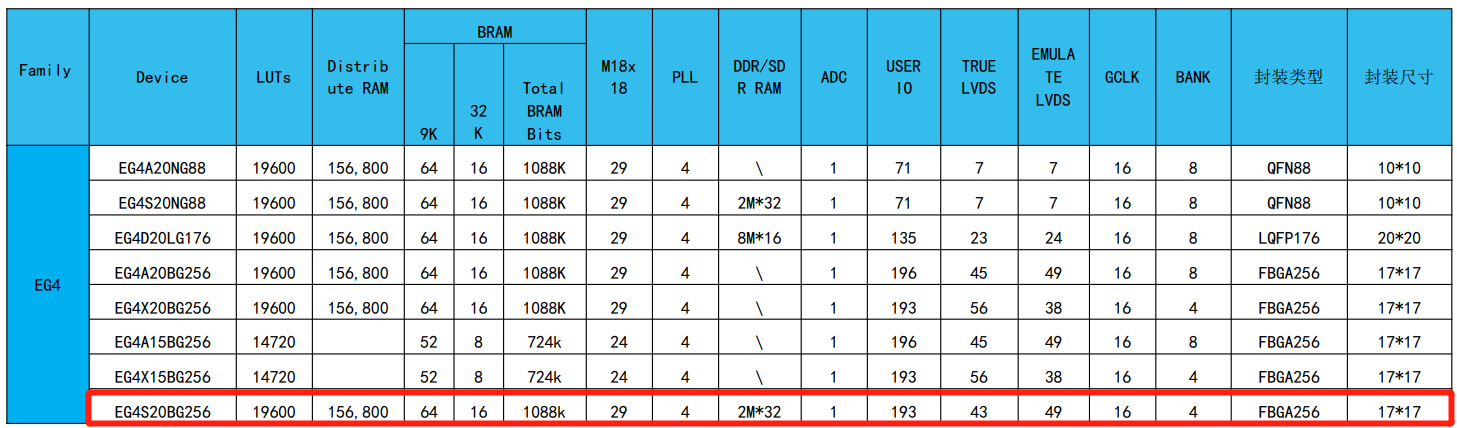

本实验平台选定芯片型号为EG4S20BG256,256个管脚(其中可用IO共193个),是基于安路成熟可靠的低成本、低功耗可编程

FPGA—EG4X20,采用最新的 3D 合封技术,与一块 2M X 32bits 的 SDRAM

合封而成。具体芯片资源如图1.3所示。

图1.3 EG4系列器件资源

EG4S20BG256的特色优势包括:

灵活的逻辑结构

· 19600个 LUTs,用户IO数量193个

低功耗器件

· 先进的55nm低功耗工艺

· 静态功耗低至5mA

支持分布式和嵌入式存储器

· 156 Kbits分布存储器(Distribute RAM)

· 1 Mbits嵌入块存储器(Block RAM简称BRAM)包括:

- 64个9 Kbits BRAM,可配置为真双口,8Kx1到512x18模式

- 16个32 Kbits BRAM,可配置为真双口,可设置为2K*16或4K*8

- 专用FIFO控制逻辑

内置大容量存储器

· 内置2M*32bits SDR SDRAM,最高工作时钟200MHz

可配置逻辑模块(PLBs)

· 优化的的LUT4/LUT5组合设计

· 双端口分布式存储器

· 支持算数逻辑运算

· 快速进位链逻辑

源同步输入/输出接口

· 输入//输出单元包含DDR寄存器

· Generic DDRx1

· Generic DDRx2

高性能,灵活的输入/输出缓冲器

· 支持LVTTL、LVCMOS (3.3/2.5/1.8V/1.5/1.2V)、PCI

· 支持LVDS,Bus-LVDS, MLVDS, RSDS, LVPECL

· 支持热插拔

· 可配置上拉/下拉模式

· 片内100欧姆差分电阻

时钟资源

· 针对高速I/O接口设计的2路IOCLK

· 16路全局时钟

· 支持4个PLLs用于频率综合

· 5路时钟输出

· 分频系数1到128

· 支持5路时钟输出级联

· 动态相位选择

配置模式

· 主模式串行SPI (MSPI)

· 从模式串行 (SS)

· 主模式并行x8 (MP)

· 从模式并行x8 (SP)

· JTAG模式 (IEEE-1532)

每个芯片拥有唯一的64位DNA

嵌入式硬核IP

· 8通道12位1MSPS SAR ADC

· 集成电压监控模块

· 内置环形振荡器

1.3 外围功能模块介绍

在FPGA的芯片型号和配置方式确定后,就需定下开发板的外围功能模块的设计方案,本DMZ_Anlogic开发板的外围功能模块包含操作类、显示类、音频类、外部晶振时钟、IO扩展口类、存储器类、协议接口类和电源这几个方面。下面将依次对这几类做一个介绍。

1.3.1 输入操作类模块

此类模块主要用于向系统输入中断信号或操作信号,包含拨动开关和按键开关。

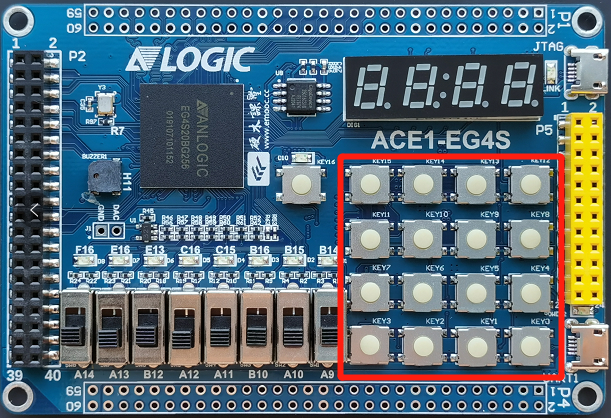

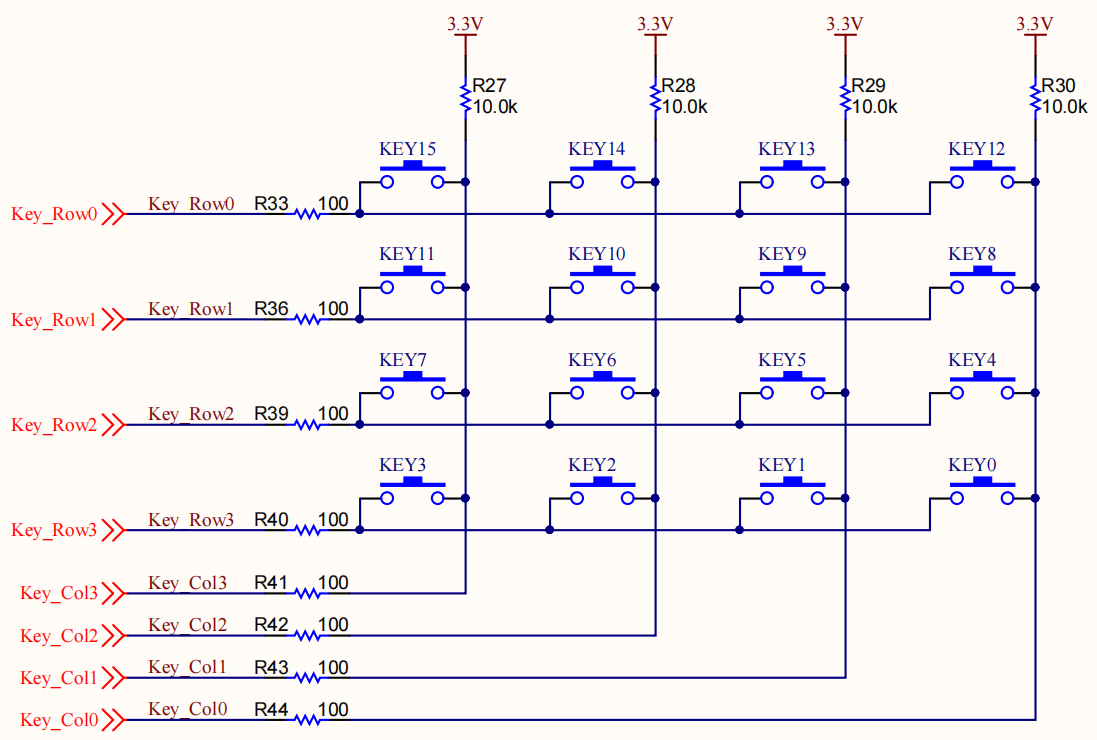

- DMZ_Anlogic开发板提供了4*4矩阵键盘,实物和原理图如图1.10所示。

图1.10 4*4矩阵按键

开关连接电路图

| 信号名 | FPGA 引脚号 |

|---|---|

| Key_Col[3] | F10 |

| Key_Col[2] | C11 |

| Key_Col[1] | D11 |

| Key_Col[0] | E11 |

| Key_Row[0] | D9 |

| Key_Row[1] | F9 |

| Key_Row[2] | C10 |

| Key_Row[3] | E10 |

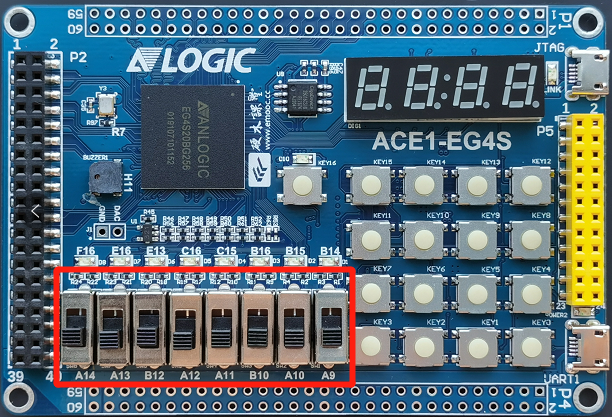

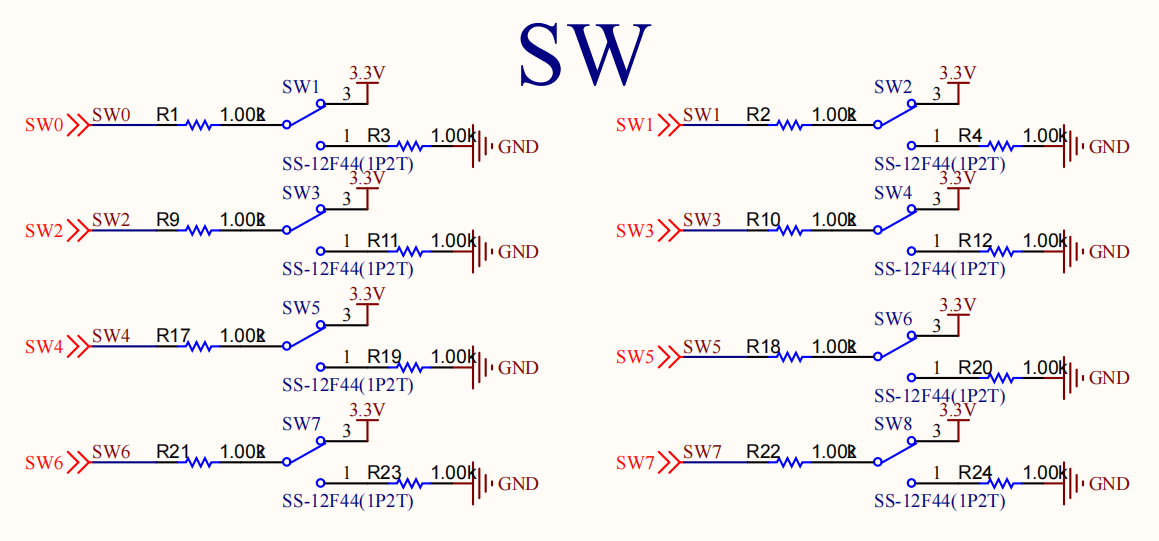

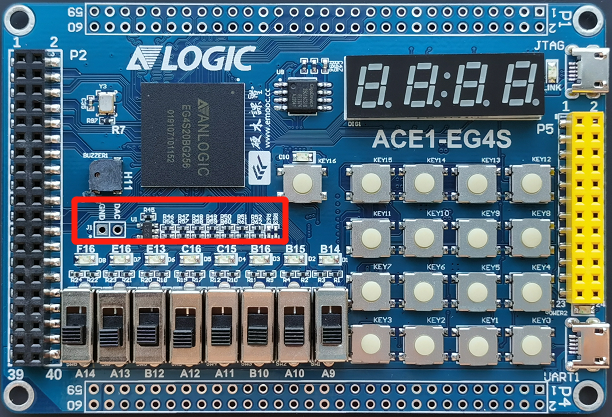

(2)DMZ_Anlogic开发板上还有8个拨动开关SW7-SW0,如图1.11所示。当拨动开关处在 DOWN

位置(靠近开发板边缘)时向FPGA相应引脚输入低电平,当拨动开关在 UP

位置时向FPGA相应引脚输入高电平。

表1.1和表1.2分别给出了按键开关和拨动开关的各个引脚连接信息。

图1.11 拨动开关连接电路图

表1.1 按键开关引脚配置

表1.2 拨动开关引脚配置

| 信号名 | FPGA 引脚号 | 原理图网络标号 |

|---|---|---|

| SW_In[0] | A9 | SW0 |

| SW_In[1] | A10 | SW1 |

| SW_In[2] | B10 | SW2 |

| SW_In[3] | A11 | SW3 |

| SW_In[4] | A12 | SW4 |

| SW_In[5] | B12 | SW5 |

| SW_In[6] | A13 | SW6 |

| SW_In[7] | A14 | SW7 |

1.3.2 输出显示类模块

此类模块主要用于将实验结果通过指示灯或显示器表现出来,包含LED灯和数码管。

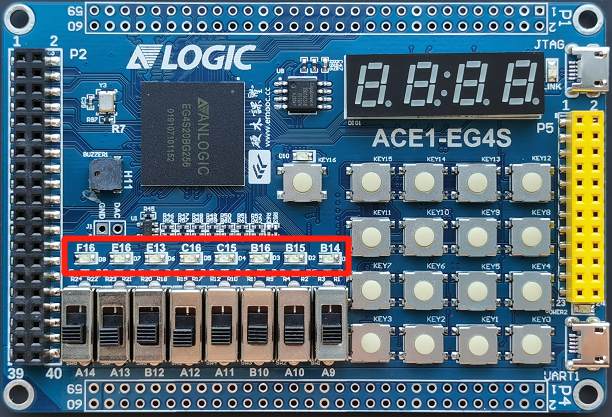

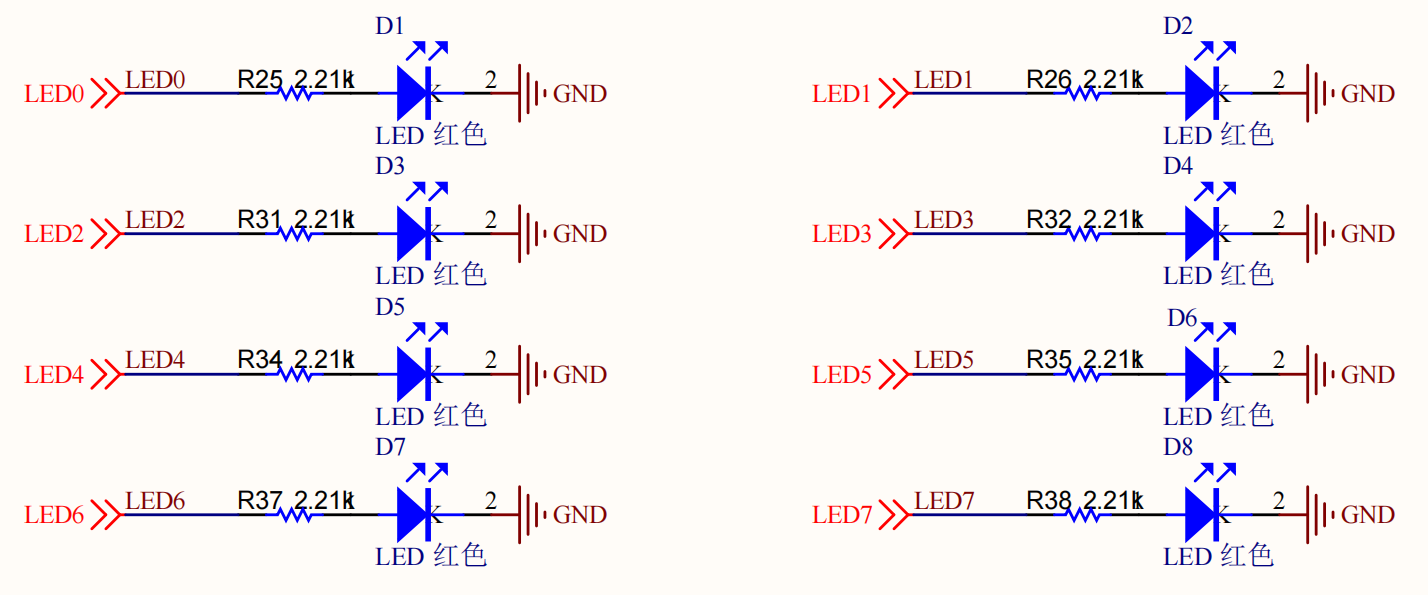

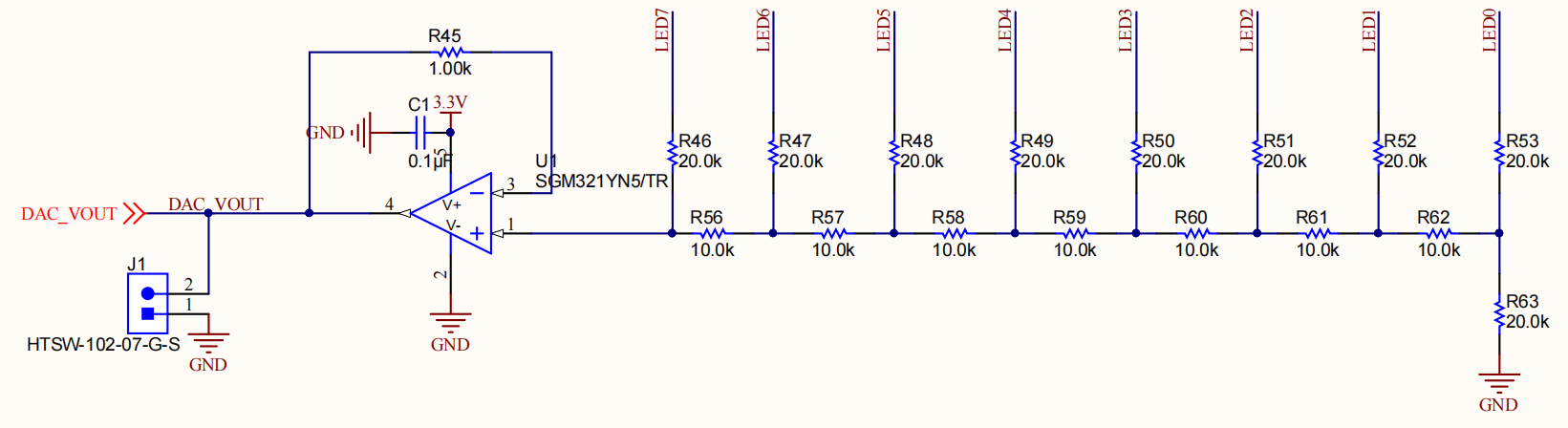

- DMZ_Anlogic开发板提供了8个直接由FPGA控制的LED灯LED7-LED0,每一个LED灯都由FPGA芯片的一个引脚直接驱动,如图1.12所示。当FPGA输出高电平时LED灯点亮,反之则熄灭。表1.3给出了LED的各个引脚连接信息。

图1.12 LED灯连接电路图

表1.3 LED引脚配置

| 信号名 | FPGA 引脚号 | 原理图网络标号 |

|---|---|---|

| LED_Out[0] | B14 | LED0 |

| LED_Out[1] | B15 | LED1 |

| LED_Out[2] | B16 | LED2 |

| LED_Out[3] | C15 | LED3 |

| LED_Out[4] | C16 | LED4 |

| LED_Out[5] | E13 | LED5 |

| LED_Out[6] | E16 | LED6 |

| LED_Out[7] | F16 | LED7 |

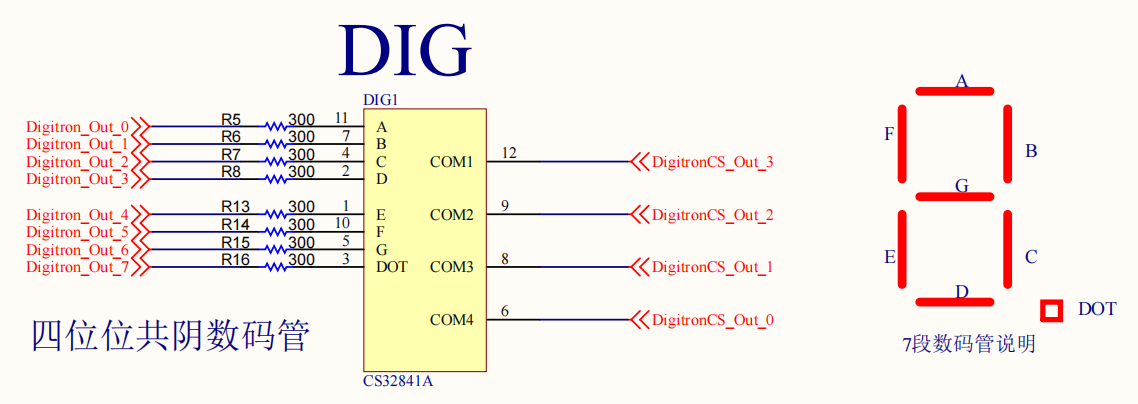

(2)DMZ_Anlogic开发板上配有一个四位七段数码管,每个数码管都由一个专用片选信号DigitronCS_Out[3:0]

控制 (因此当正放DMZ_Anlogic开发板时,从右至左依次为DIG0

-DIG3),如图1.13所示,片选信号直接与FPGA引脚相连,当FPGA输出低电压时,对应的数码管选中,反之则不选中。七段数码管的每个引脚(共阴模式)均连接到

FPGA

芯片上,当FPGA输出高电压时,对应的字码段点亮,反之则熄灭。表1.4给出了数码管的各个引脚连接信息。

图1.13 数码管连接电路图

表1.4 数码管引脚配置

| 信号名 | FPGA 引脚号 | 说明 |

|---|---|---|

| Digitron_Out[0] | A4 | 字码段A |

| Digitron_Out[1] | A6 | 字码段B |

| Digitron_Out[2] | B8 | 字码段C |

| Digitron_Out[3] | E8 | 字码段D |

| Digitron_Out[4] | A7 | 字码段E |

| Digitron_Out[5] | B5 | 字码段F |

| Digitron_Out[6] | A8 | 字码段G |

| Digitron_Out [7] | C8 | 字码段DOT |

| DigitronCS_Out[0] | C9 | COM4(最右的位) |

| DigitronCS_Out[1] | B6 | COM3 |

| DigitronCS_Out[2] | A5 | COM2 |

| DigitronCS_Out[3] | A3 | COM1(最左的位) |

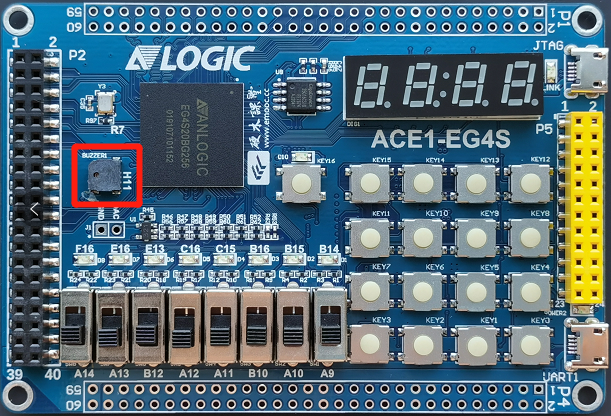

1.3.3 音频或发声类模块

此类模块主要用于系统报警器或发声功能,包含一个无源蜂鸣器。

(1)DMZ_Anlogic开发板上配有一个无源蜂鸣器,经过功率放大电路后与FPGA的引脚相连,如图1.14所示。通过改变FPGA芯片输出高低电平翻转的频率可以调节蜂鸣器的发声频率。

表1.5给出了蜂鸣器的引脚连接信息。

图1.14 蜂鸣器连接电路图

表1.5 蜂鸣器引脚配置

| 信号名 | FPGA 引脚号 | 说明 |

|---|---|---|

| Buzzer_Out | H11 | 蜂鸣器 |

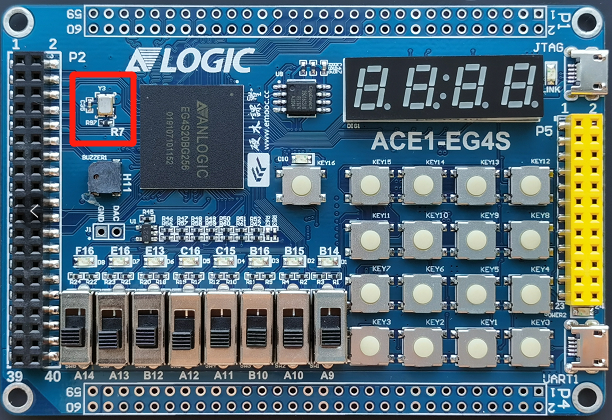

1.3.4 时钟模块

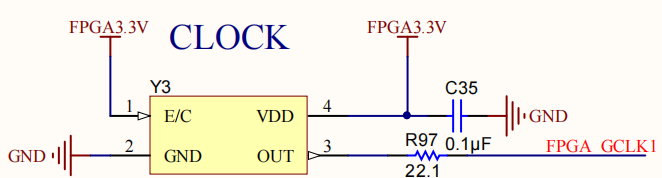

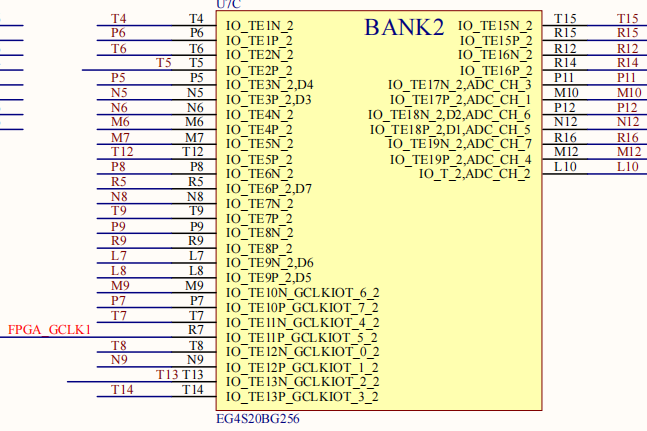

DMZ_Anlogic开发板上包含一个生成50MH频率时钟信号的晶体振荡器,如图1.15所示。该时钟信号直接与FPGA芯片引脚相连,用来驱动FPGA内部的用户逻辑电路。表1.6给出了时钟信号的引脚连接信息。

图1.15 晶体振荡器连接电路图

表1.6 时钟信号引脚配置

| 信号名 | FPGA 引脚号 | 说明 |

|---|---|---|

| CLK | R7 | 50 MHz时钟源 |

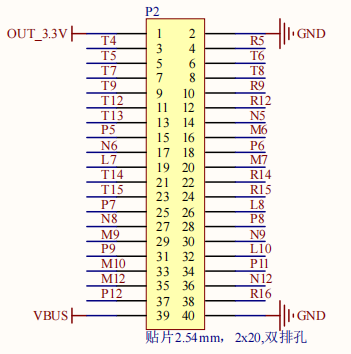

1.3.5 IO拓展口模块

此类模块主要用于向系统输入信号或输出由系统产生的信号。

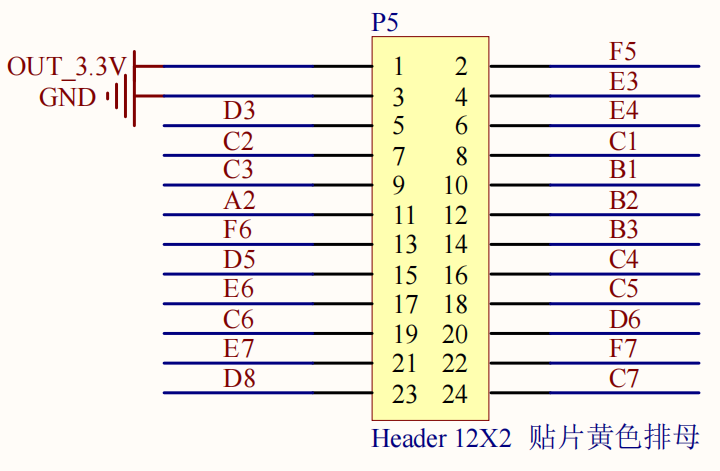

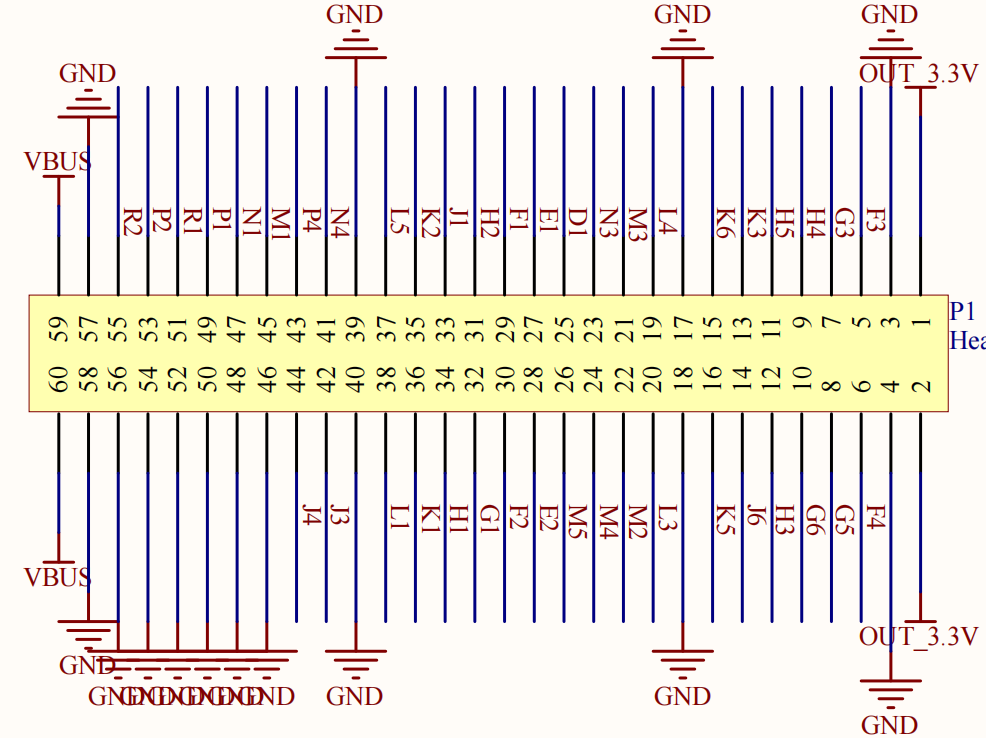

- DMZ_Anlogic开发板上提供了多个扩展IO的插座。

左侧40针,可插接高速AD/DA模块、摄像头模块等

右侧24针,可插接并口LCD模块

上方2*30排孔,其中有6对LVDS差分对

下方2*30排孔,其中有6对LVDS差分对

图1.16 通用IO口引脚连接电路图

1.3.6 R-2R DAC模块(复用LED引脚)

与LED引脚复用的是一路8位R-2R型DAC,可以利用R-2R电阻网络将FPGA

IO输出的8位高电平(3.3V)或低电平(0V)输出转换为256级模拟电压。用作DAC和DDS部分的实验内容。DAC的输出电压与FPGA的输出码值DA_Data[7:0]关系为:

DAC_VOUT = 3.3V * DA_Data[7:0]/256

| 信号名 | FPGA 引脚号 | 原理图网络标号 |

|---|---|---|

| DA_Data[0] | B14 | LED0 |

| DA_Data[1] | B15 | LED1 |

| DA_Data[2] | B16 | LED2 |

| DA_Data[3] | C15 | LED3 |

| DA_Data[4] | C16 | LED4 |

| DA_Data[5] | E13 | LED5 |

| DA_Data[6] | E16 | LED6 |

| DA_Data[7] | F16 | LED7 |

1.3.7 UART通信模块

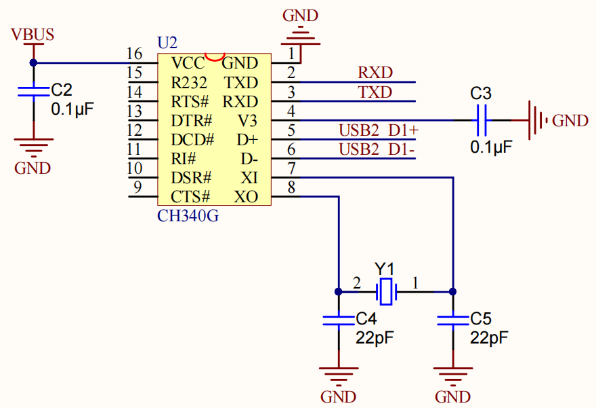

DMZ_Anlogic开发板上集成了一个UART转USB的转接电路,如图1.21所示。这使得FPGA板卡与PC机进行数据交互变得简单,直接使用USB数据线将PC机与开发板上的UART接口(见图1.1)相连,USB数据经过此电路后转化为UART协议的形式进入FPGA中。

需要注意的是,图1.21中的TXD引脚是由该电路向FPGA芯片发送UART协议的数据,RXD引脚是由该电路接收由FPGA芯片向外部发送的UART协议的数据,在配置引脚时需搞清数据传输方向。表1.7给出了进行UART通信实验时FPGA的引脚连接信息。

图1.21 USB转UART连接电路图

表1.7 UART通信引脚配置

| 信号名 | FPGA 引脚号 | 说明 |

|---|---|---|

| RXD | F12 | FPGA接收外部数据 |

| TXD | D12 | FPGA向外部发送数据 |