大拇指安路FPGA开发板——我的第一个工程

基于FPGA的数字实验指导书

(Anlogic EG4S20BG256版本)

TangDynasty®(TD)软件是安路科技自主开发的FPGA集成开发环境,支持工业界标准的设计输入,包含完整的电路优化流程以及丰富的分析与调试工具,并提供良好的第三方设计验证工具接口,为所有基于安路科技FPGA产品的应用设计提供有力支持。

以下是在TD中建立流水灯工程并下载到DMZ_Anlogic开发板中验证的全过程:

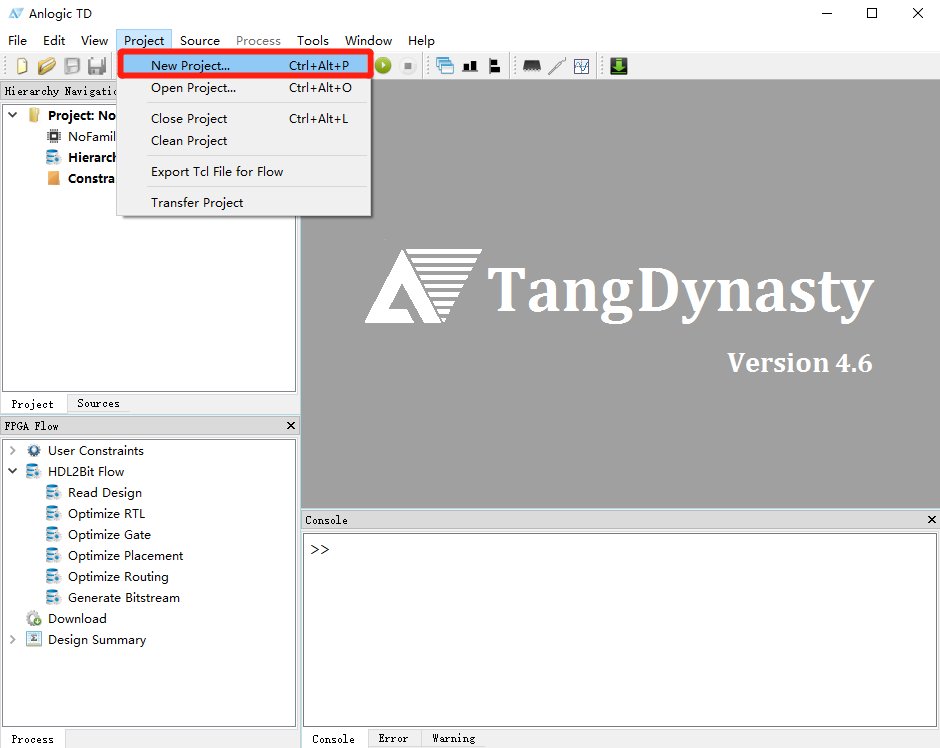

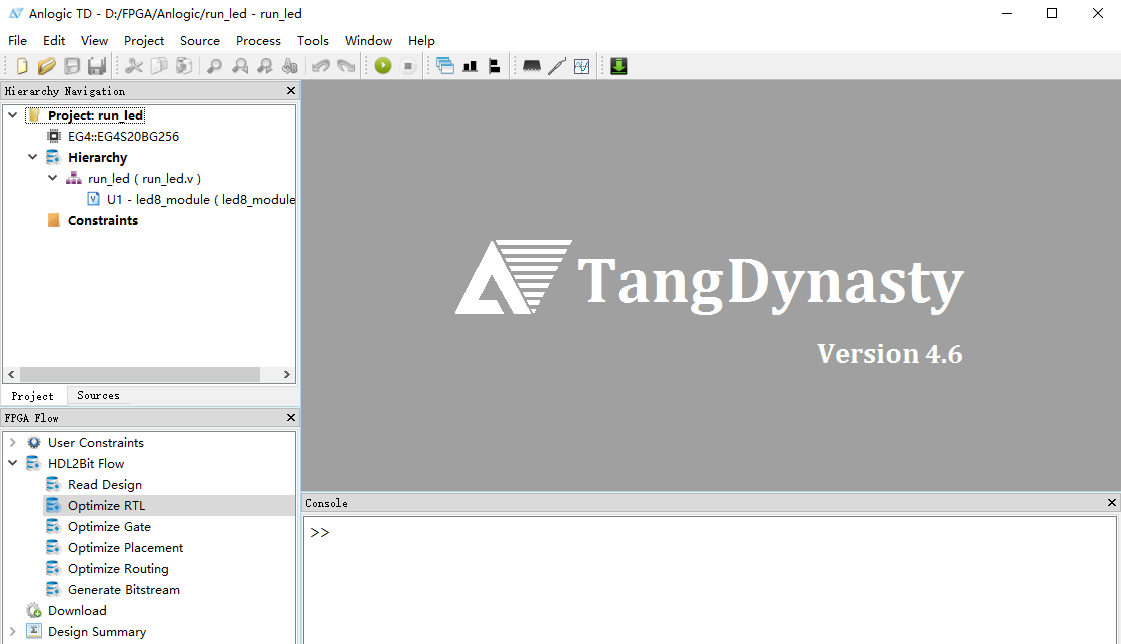

1、新建工程。如图1.23所示,打开TD然后点击红圈处的按钮,即可新建一个工程。

图1.23 新建工程

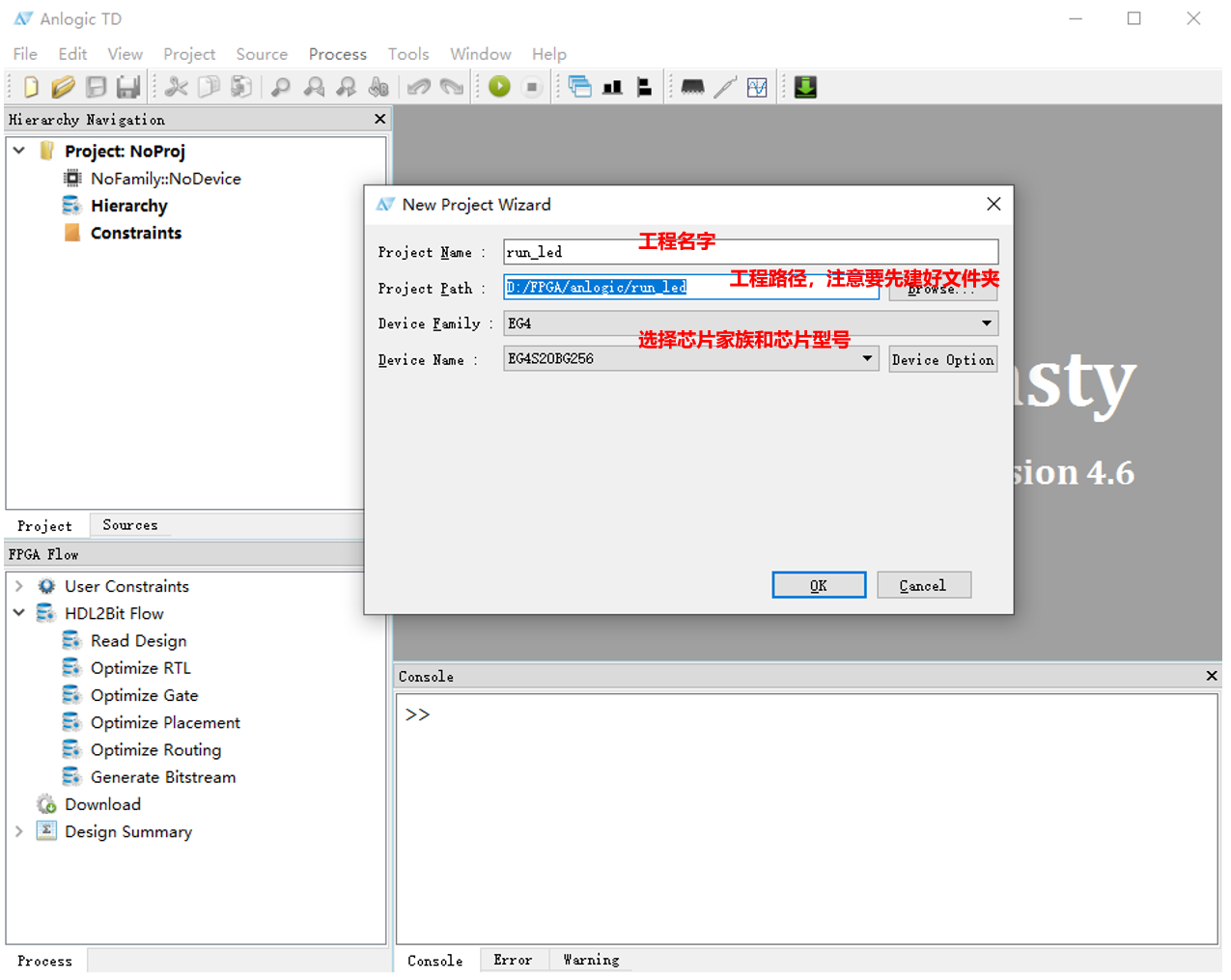

2、确定工程名。如图1.24所示,在打开的对话框中分别选择工程路径,设置工程名字。这里我的工程路径是D:/FPGA/anlogic/run_led,这里需要注意的是文件夹必须先自行建好,否则软件会报错“路径不存在”,另外TD的路径中不能出现中文名。接下来的工程名和顶层文件名取run_led,然后点击“Next”。

图1.24 建立工程

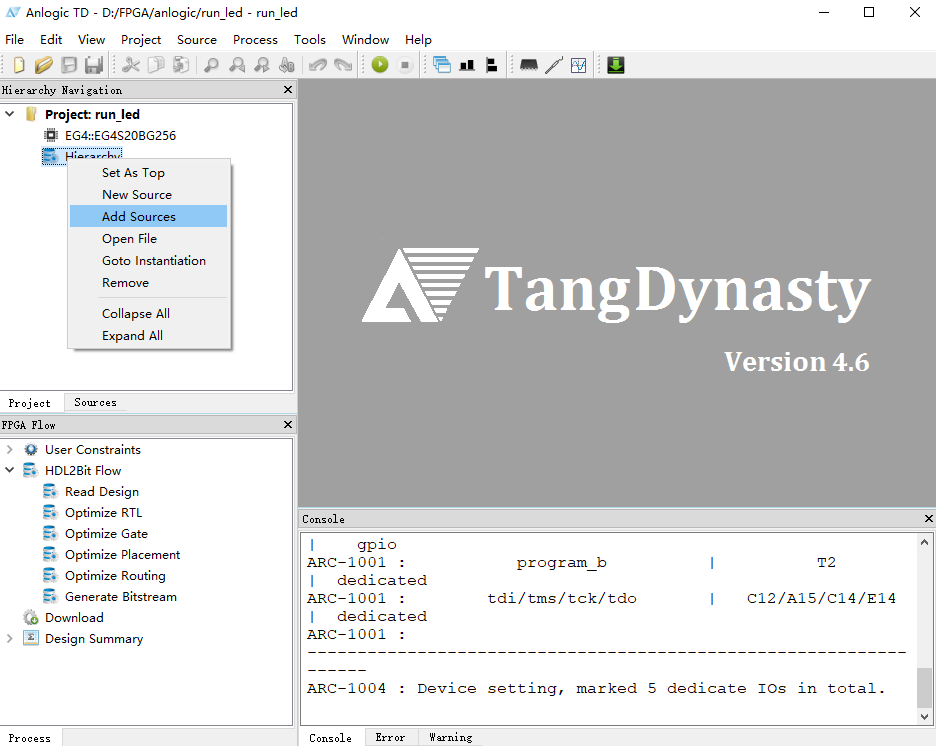

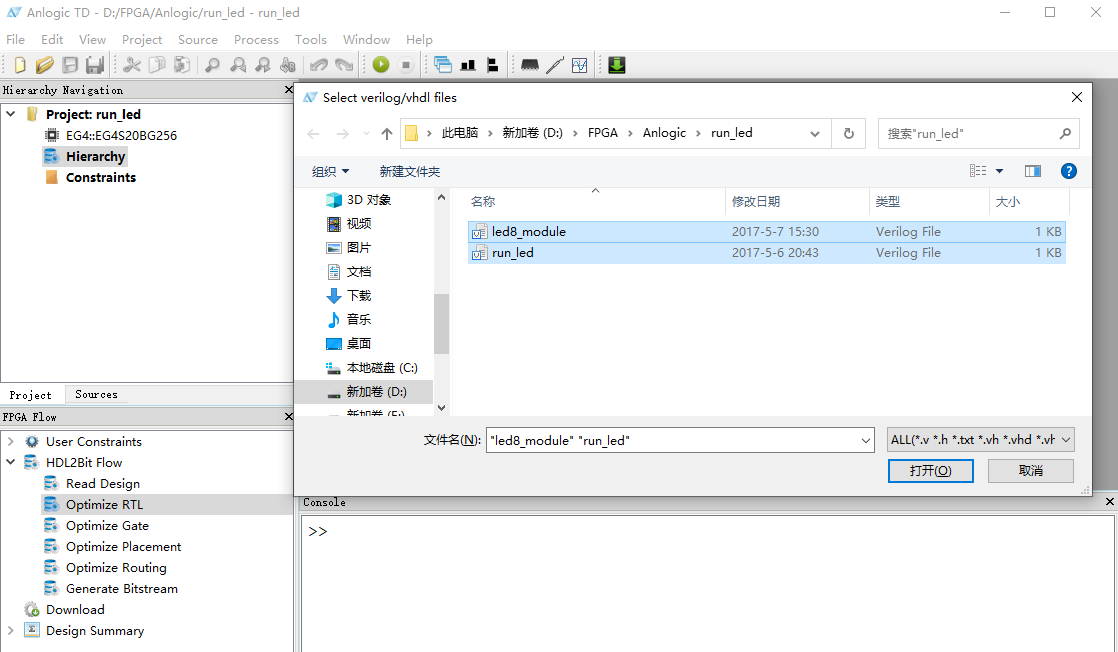

3、添加已有的设计文件或新建设计文件。如图1.25所示,在这里我们选择添加现有的设计文件(事先将要使用的.v文件拷贝到工程文件夹下):

图1.25 添加已有的设计文件

添加已有的设计文件后,TD软件会自动识别顶层文件并将其设置为“Top”

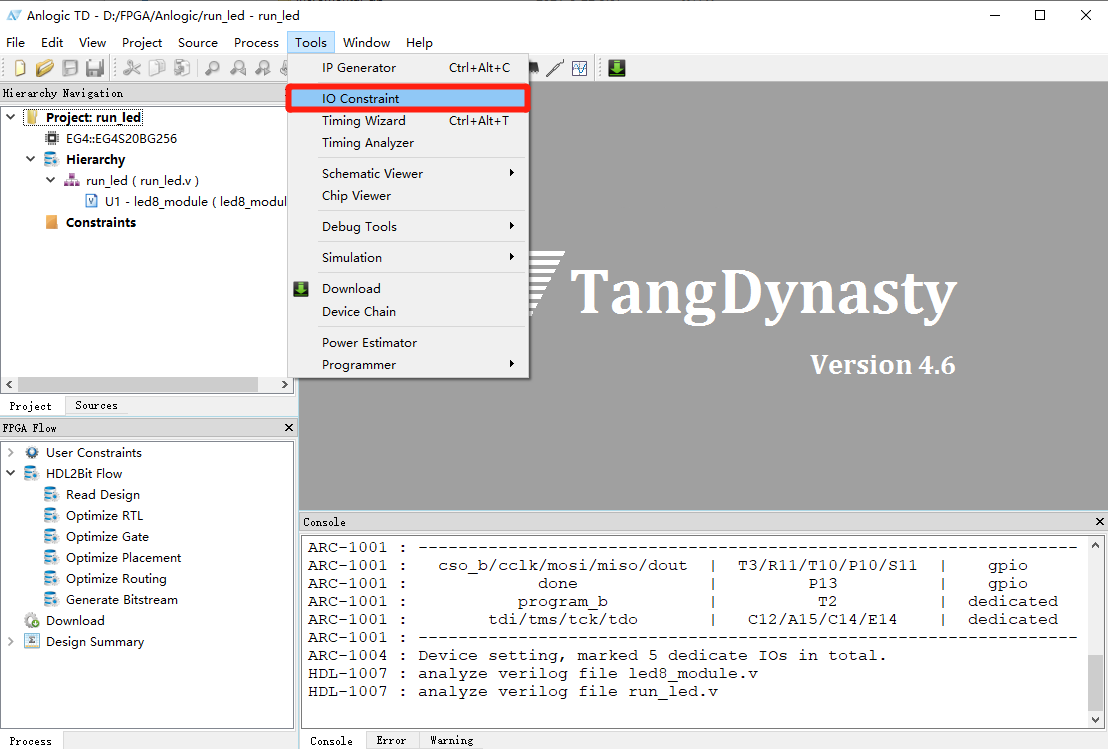

4、分配引脚,点击Tools下面的IO Constraint调出IO分配界面,如图1.26。

图1.26 调出引脚分配界面

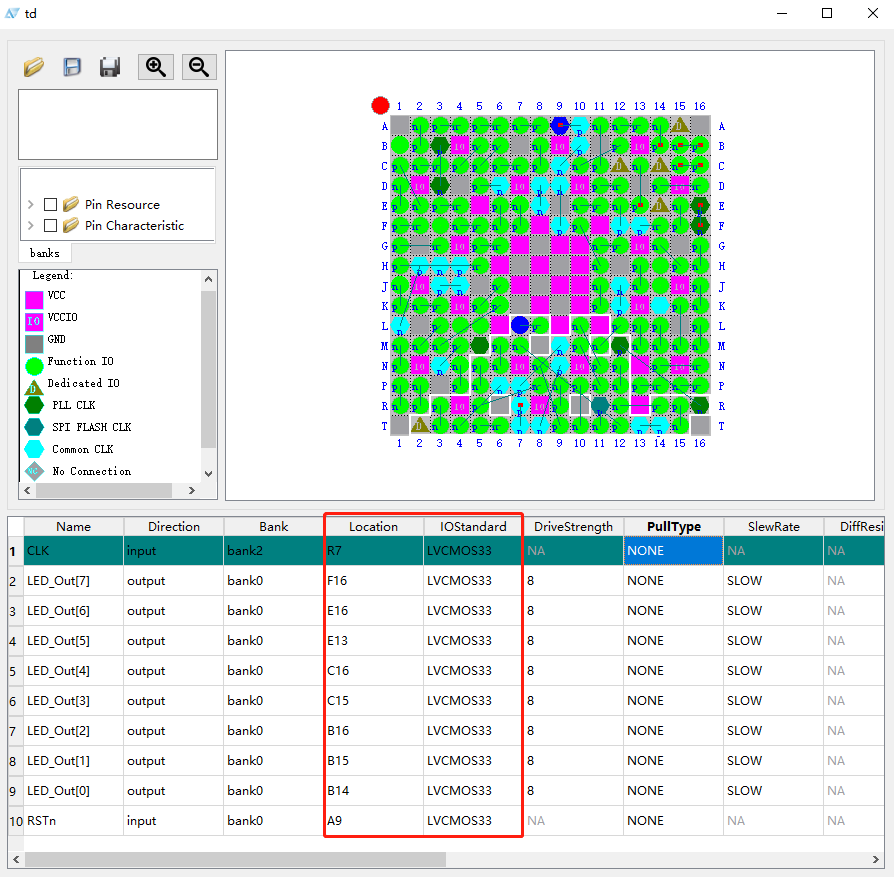

图1.27 分配引脚

这里需要根据原理图的硬件连接关系分配引脚,点击保存TD会将图形化设置保存为xxx.adc文件(需自定义文件名),并自动将该adc文件(Anlogic Design Constrain)添加到工程中。

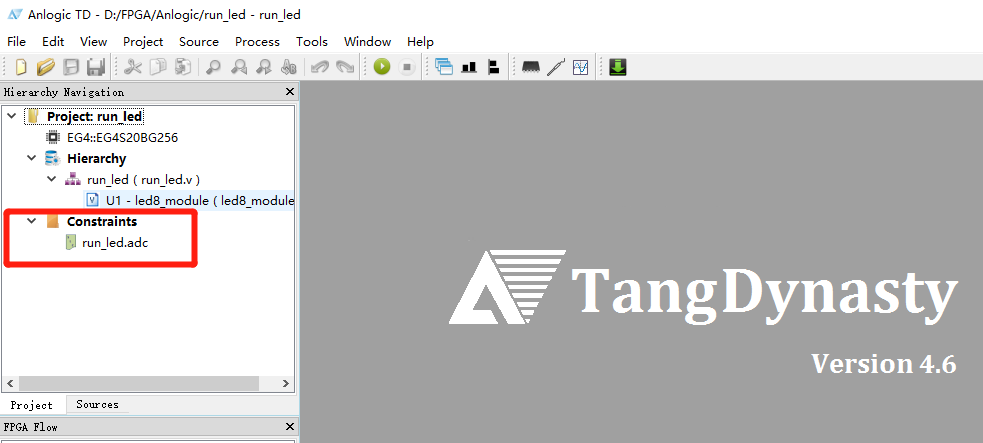

图1.28 保存为adc文件并添加到当前工程

后续设计,也可以直接修改adc文件,并手动将adc文件添加到工程下。例如下面是刚才生成的adc文件,可以根据新的工程手动修改网络名和IO位置,另存后给其他工程使用。

set_pin_assignment { CLK } { LOCATION = R7; IOSTANDARD = LVCMOS33; PULLTYPE = NONE; }

set_pin_assignment { LED_Out[0] } { LOCATION = B14; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[1] } { LOCATION = B15; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[2] } { LOCATION = B16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[3] } { LOCATION = C15; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[4] } { LOCATION = C16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[5] } { LOCATION = E13; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[6] } { LOCATION = E16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { LED_Out[7] } { LOCATION = F16; IOSTANDARD = LVCMOS33; }

set_pin_assignment { RSTn } { LOCATION = A9; IOSTANDARD = LVCMOS33; PULLTYPE = NONE; }

这样我们第一个工程就已经建好,接下来我们需要编译工程(大拇指安路FPGA开发板——编译和下载),生成.bit文件,写入芯片进行验证。